概要

EZ-FPGAにカメレオンUSB用ロジアナ基板を乗せて、PROMエミュレータとして動作させるものです。

現状は、

カメレオンUSB版PROMエミュレータからの移植ですが、下記の点が異なっています。

・動作が安定していて、PBSRAMを最大133MHzで駆動できる。

・PBSRAMのクロックを50MHz〜133MHzまで、1MHz単位で変更可能

・回路規模は全体の14%で、将来的にさまざまな付加機能を追加可能

・CPLDの書き込みなど、セットアップ作業が不要

・転送速度が遅い。(EZ-USBのシリアル転送速度の問題)

特徴

・カメレオンUSB+ロジアナ基板をそのまま流用可能

・64Kbit〜4MBitまでの一般的なDIP28/DIP32ピンのROMに対応

・一部のFlashROMにも対応、ただしの通常リード機能のみ

・5.0V TTLレベルの他、3.3V LVCMOSレベルにも適合

・特定アドレスのアクセスを検出できるアクセストリガ機能

・ダウンロード中にターゲットのRESET信号を制御可能

PBSRAMの動作クロック変更機能による、消費電流制御機能

・Win32コンソールプログラム

・エミュレーション動作中のリアルタイムダウンロード不可

・単体バックアップ機能無し

将来的に追加可能な機能としては

・エミュレーション中のリアルタイムダウンロード

・内蔵BlockRAMを使用した、アクセスヒストリー機能

・LowPinCount(LPC)バス FlashROMのサポート

・FlashROMの書き込み/イレース動作のエミュレーション

・トリガーバンク切り替え機能による、CPU向け疑似ハードウェアブレークポイント機能

などがあります。

ダウンロード

DIP28/32用プローブ回路図 ※「表面コネクタ仕様(標準)」に適応

Ver1.00 プログラムバイナリ

Ver1.00 プログラム/FPGAデザインソース

使い方

1.EZ-FPGAとPBSAM基板、PBSAM基板とプローブ、プローブとターゲットを接続します。

2.EZ-FPGAとMINI-EZUSBを接続してPCのUSBポートに接続します。

3.ezfrome.exeをWindowsのコマンドプロンプトから実行して、データをダウンロードします。

形式:ezfrome.exe {オプション...} [ファイル名]

[ファイル名]:転送するROMデータ、バイナリ形式

{オプション} -r[ROMタイプ] = ROMタイプ設定

2764,27128,27256,27512,27010,27020,27040,29040 から選択

-a = すべてのROMエリアを書き込む(省略時はファイル長にあわせる)

-p[PADコード] = PADコードを16進数で指定(省略時 0ffH)

-ts[アドレス] = シングルトリガ、アドレス設定

-tp[アドレス] = パルストリガ、アドレス設定

-tc[アドレス] = シングルトリガクリア

-s[on][off] = リセット制御、'L','H','Z'のいずれかで指定

-c[cljMHz] = PBSRAM駆動周波数、50〜133の値で指定

-w = 終了時に'HIT ANY KEY'の表示とキー入力待ちをする

※必要に応じてショートカットを作成すると便利です。

・ezfrome.exeをデスクトップ等に右ドラッグ&ドロップで、「ショートカットを作成」します。

・ショートカットを右クリックして「プロパティ」を開き、リンク先を編集します。

例1:ダブルクリックで29EE020の固定ファイルをダウンロード/実行

リンク先:[ディレクトリパス]\ezfrome.exe -w -r27020 rom_data.bin

例2:ROMファイルのドラッグ&ドロップで27C256の任意ファイルをダウンロード/実行

リンク先:[ディレクトリパス]\ezfrome.exe -w -r27256 %1

※ROMデータのHEX-BIN変換等が必要な場合は、バッチファイルを使うと自動化ができるでしょう。

4.ターゲットの電源を入れる。

サポートROM

DIP28またはDIP32ピンで、よく使われている一般的な物に対応しています。

対応ROM一覧

| ROM名 | 形状 | 容量 | 説明 |

|---|

| 27C64 | DIP28 | 64KBit | 27C128からA13を削除したタイプ |

|---|

| 27C128 | DIP28 | 128KBit | 27C256からA14を削除したタイプ |

|---|

| 27C256 | DIP28 | 256KBit | 古くからごく一般的に使われているもの |

|---|

| 27C512 | DIP28 | 512KBit | 1pinがA15で、他が27C256と同じタイプ |

|---|

| 27C010/29F010 | DIP32 | 1MBit | 27C512をDIP32に延長した感じ,A16=2pin,(WE=31pin) |

|---|

| 27C020/29F020 | DIP32 | 2MBit | 27C010/29F010にA17を追加したもの、A17=30pin |

|---|

| 27C040 | DIP32 | 4MBit | 27C020にA18を追加したもの、A18=31pin |

|---|

| 29F040 | DIP28 | 4MBit | 29F020にA18を追加したもの、A18=1pin |

|---|

・PROM,FlashROMともに書き込み動作には未対応です。

特に27Cxxxシリーズや28Fxxxシリーズでは書き込み厳禁です。+12Vが印可されカメレオンUSBが壊れます

・FlashROMは、デバイスIDの読み込み等も未対応です。

・1Mbitはピン配置の違う物(マスクROMとコンパチ)がたまにあるので特に注意

・信号レベルは3.3V LVCMOレベルですが、5.0V TTLレベルにも適合します。

・ROMのVCC端子電圧がLレベルの時は、データ出力が禁止されます。

アクセスタイム、仕様

アドレス確定−データ出力:6クロック+15ns程度 (60ns@133MHz,75ns@100MHz,135ns@50MHz)

CEアサート−データ出力:10ns程度

OEアサート−データ出力:10ns程度

アクセストリガー感度:2xクロック

トリガポイント位置遅延:3xクロック + α

トリガパルス最小幅:1xクロック

※PBSRAMの駆動周波数により、アクセス速度等は変化します。

アドレス確定に対する最大アクセス時間は、アドレスSetupTime+サンプリングディレイ1クロック+メモリアクセス3クロック+出力遅延となります。

CEとOEに対するアクセス時間は3ステート制御の論理ゲートだけです。

アクセストリガーの検出は、2サンプルのコンペアを取っています。出力信号は、さらに1クロック後にラッチ出力されます。

消費電流

約275mA @100MHz

約353mA @133MHz

いづれも、MINI-EZUSBを除いた、EZ-FPGA+4MBit PBSRAMの常温での実測値

※PBSRAMの駆動周波数やターゲットのターミネート回路により消費電流は変動します。

プローブ回路の説明

基本的には32本のプローブ用信号にROMのピンを繋ぐだけですが、EZ-FPGAの電源がOFFの時にFPGAのピンに電圧が印可されると、FPGAが壊れる危険性があります。

そこで、直列に抵抗を入れることで電流制限を行っています。

使用方法を絶対間違わなければ抵抗を省略できますが、面倒でも抵抗の挿入を強くお勧めします。

VPPになる端子にはプログラム時に+12.5V等が印可されるため、抵抗が入っていてもかなり危険です。そこでツェナーダイオードで端子電圧が5.1V以上にならないように保護しています。(ただしVPP=12Vを加えて良いわけではない)

ターゲットに書き込み機能がなければ、VPP保護は不要でしょう。

プローブとヘッダの方向が逆になっていますが、これはDPI32の16ピンをGNDに落とす必要があることと、DIP28の時にGNDピンを共有するためこの方向にしてあります。

ICソケットの16,17pin側にはみ出した部分をプローブ用コネクタの1ピン(GND)にあわせるようにします。これでDIP32の17ピンがPROBE0,16ピンがPROBE1と全ピンが順番につながります。※裏だしの場合

27C512以下のDIP28で使用する場合、DIP32の1,2,31,32ピンを余らせるようにして、DIP28ソケットを装着することで対応可能です。

作成したPROMプローブは、40芯のキーピンのないIDEケーブルでカメレオンUSBロジアナのプローブ用コネクタに接続します。※EIDE用80芯ケーブルも使えません

EZ-FPGA制御仕様

JTAG_MEMのアドレス空間に、エミュレーションRAMとコントロールレジスタをマップしています。

00000000H-03FFFFFFHはエミュレーションRAMに直結で、EMUビット=0の時にリード/ライトが可能です。書き込みデータは一度ラッチされ、DWORD単位で書き込みます。

40000000H-07FFFFFFHには、コントロールレジスタがマップされています。

書き込みレジスター(FWR=L)

| JA(アドレス) | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | 内容 |

|---|

| 40000001h | A7 | A6 | A5 | A4 | A3 | A2 | --- | --- | トリガアドレス |

| 40000002h | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | トリガアドレス |

| 40000003h | --- | --- | --- | --- | --- | A18 | A17 | A16 | トリガアドレス |

| 40000005h | P7 | P6 | P5 | P4 | P3 | P2 | P1 | P0 | PLL分周費-1(周波数) |

| 40000006h | EMU | RSE | RSL | TPM | --- | --- | --- | --- | モード設定 |

| 40000007h | --- | F18 | R18 | R17 | R16 | R15 | R14 | R13 | ROM選択、注1 |

注1:R13〜R18,F18でアドレスの有効/無効を設定することでROMを選択する

読み込みレジスター(FRD=L)

| JA(アドレス) | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | 内容 |

|---|

| 40000000h | RD7 | RD6 | RD5 | RD4 | RD3 | RD2 | RD1 | RD0 | ヒストリデータリード(未実装) |

| 40000001h | A7 | A6 | A5 | A4 | A3 | A2 | --- | --- | トリガアドレス |

| 40000002h | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | トリガアドレス |

| 40000003h | --- | --- | --- | --- | --- | A18 | A17 | A16 | トリガアドレス |

| 40000004h | '0' | '0' | '0' | '0' | DLL | PLL | VCC | TRG | ステータス |

| 4000000ch | '0' | '1' | '0' | '1' | '0' | '0' | '1' | '0' | CPLDチェックコード'R' |

| 4000000dh | '0' | '1' | '0' | '0' | '0' | '1' | '0' | '1' | CPLDチェックコード'E' |

| 4000000eh | '0' | '1' | '0' | '0' | '0' | '1' | '1' | '0' | CPLDチェックコード'F' |

| 4000000fh | '0' | '0' | '0' | '1' | '0' | '0' | '0' | '0' | Version 10h |

ソフトウェアの仕様

EZ-FPGAライブラリを使用しています。

FPGAコンフィグ前にチェックコードをアクセスして、すでに起動している時には再コンフィグしないようにしています。

FPGAコンフィグ後の制御は、すべてJTAG_MEMで行っています。

動作確認

・FPGA-PACMAN (27020)

・Xeltek SUPERPRO/LX (Universal Writer)

SST 29EE2020 (27020)

※ユニバーサル/ROMライタによる動作確認は、危険なのでお勧めしません。

・秋月H8ボード(シーエー様にてBeta版をご使用)

DIP28/DIP32対応PROMプローブの制作例

0.回路図を良く確認します。

回路、部品構成、大きさ、製作順番などを頭のなかでしっかり組み立てます。

特に、プローブ部分は小さくまとめないと、ターゲットの部品と干渉を起こすことがあります。

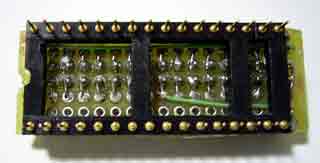

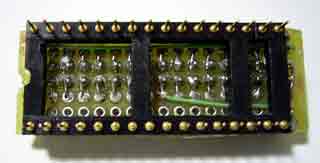

1.32ピンのヘッダーピンを、適当にカットした基板に取り付けます。

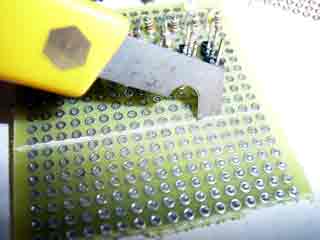

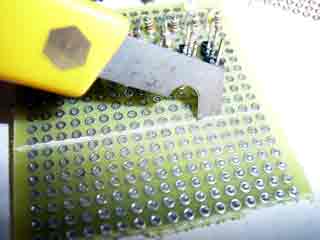

※秋月C基板を、Pカッターなどで横に切断するとちょうど良いサイズです。

ヘッダピンの3ピンと、DIP32の16ピンが合う位置にヘッダピンをマウントします。

※RESETやTRIGGERを使用する場合やサイズが気にならない方は、IDE等で使われている逆ざし防止機能つきの40ピンボックスヘッダもお勧めです。

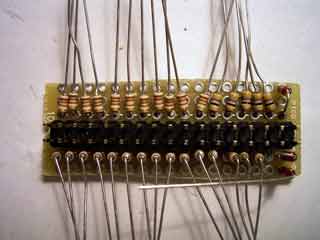

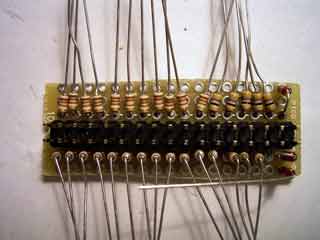

2.保護抵抗とツェナーダイオードを基板に取り付けて半田付けします。

抵抗の取り付け位置は、ケーブル用コネクタの干渉に注意します。

チップ抵抗を使うと見た目も綺麗ですっきりすると思います。私はオシロやロジアナのプローブでつまみたかったのでリードタイプで作りました。

※ツェナーダイオードとヘッダピンの配線も行います。(写真は配線前)

※VPPプログラム電圧保護が不要なら、ツェナーダイオードは省略できます。

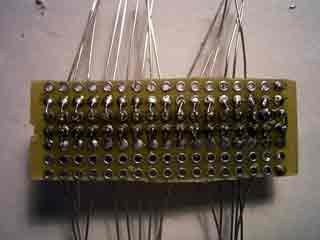

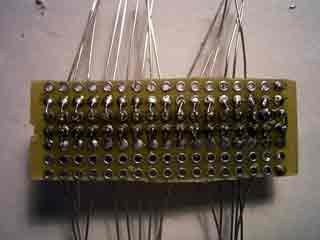

4.32ピンのピンソケットを基板に取り付け半田付けします。

※ここでは秋月電子通商のDIP40のピンを切断して使用しています。

※ICソケットを使用する場合、丸ピンではターゲットのICソケットを痛めることがあるので、平ピンの方が適しています。

5.完成です。IDE用40芯ケーブルでPB-SRAMボードと接続します。