今回はEZ-FPGAの簡単なアプリケーションとしてPLLとDLLを使用したクロックジェネレータのデザインをVerilogで作成してみます。

まずWebPackのProject Navigatorを起動します。

Windowsの「スタート -> すべてのプログラム -> Xilinx ISE 5 -> Project Navigator」で起動します。

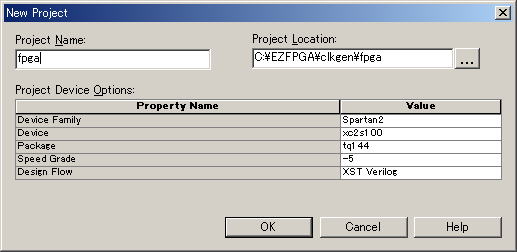

起動しましたらメインメニューの「File -> New Project」で新規のプロジェクト作成を指示します。

「Project Name」はプロジェクトの名前を入れます。今回は「fpga」にします。

「Project Location」はプロジェクトを作るディレクトリを指定します。

「Device Family」は「Spartan2」を選択してください。

「Device」は「xc2s100」を選択してください。

「Package」は「tq144」を選択してください。

「Speed Grade」は「-5」を選択してください。

「Design Flow」は「XST Verilog」を選択します。

全て入力したら「OK」です。

これでfpgaのディレクトリにプロジェクトファイル(fpga.npl)が作成されます。これ以降はこのfpga.nplをダブルクリックすることで自動的にWebPackのProject Navigatorを起動してくれます。

デザインの中身(ソース)は通常Verilogソース(拡張子.v)とピン配置ファイル(拡張子.ucf)です。

ピン配置ファイルは、SPARTAN2のピンの何番を、どのような名前の信号として使用するかを定義したものです。

VerilogなどのHDL言語では特定の機能をまとめたものをモジュールとして扱います。例えばPLLの機能を実現するVerilogのモジュールはpll.vです。このpll.vをトップレベルモジュールから呼び出して使用します。

EZ-FPGA用にオプティマイズから公開されているモジュールはpll.vの他にJTAG関連のアクセスモジュールとしてjtagspi.vとjtagmem.vがあります。

pll.vはVerilogのソースコードとして公開されますが、jgagspi.vとjtagmem.vはモジュールの定義部分(拡張子.v)とネットリストライブラリ(jgag_spi.ngc、jtagmem.ngc)として公開されます。

今回のクロックジェネレータで使用するファイルはfpga.v(トップモジュール)、fpga.ucf、pll.v、jtagmem.v、jtagmem.ngcです。

zipをおいておきますので、解凍して中身を先ほど作成されたfpgaディレクトリーにコピーしてください。

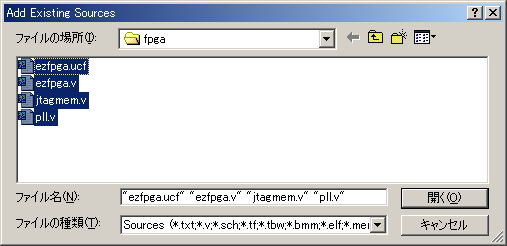

これらのファイルをプロジェクトに追加します。追加方法はメインメニューから「Project -> Add souce....」です。

この画面でピン配置ファイル(ucf)とVerilogファイル(.v)を全て選択します。

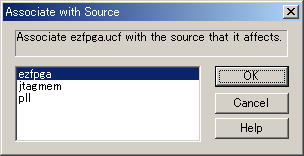

ピン配置ファイル(ucf)をどのVerilogソースと関連付けるかを聞いてきますので、トップレベルモジュールのezfpgaと答えます。

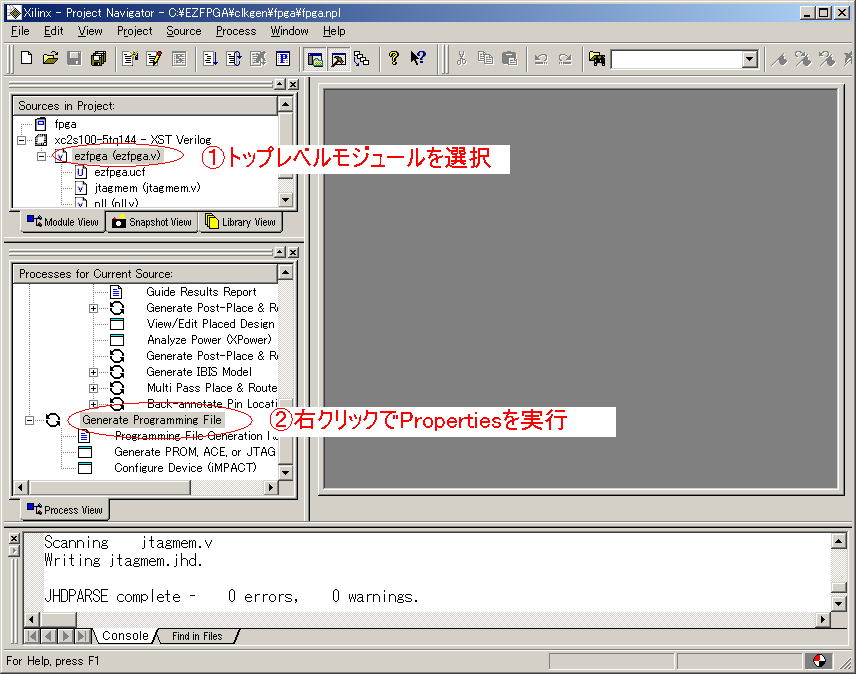

これで必要なソースファイルがプロジェクトに追加され以下の画面になります。

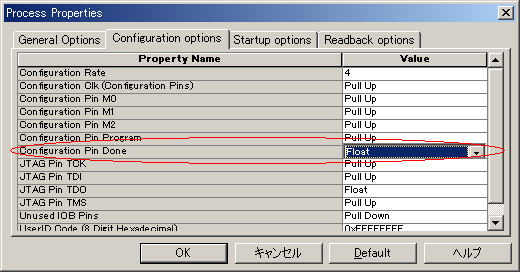

トップレベルモジュールの「ezfpga (ezfpga.v)」を選択して「Generate Programming File」のプロパティーを開きます。

「Configuration optitions」タブの「Configuration Pin Done」を「Pull Up」から「Float」に変更します。

これによりコンフィグ終了後にLD2のチップLEDが消燈するようになります。

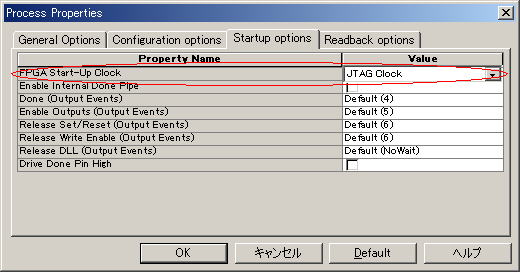

さらに「Startup options」タブの「FPGA Start-Up Clock」を「GCLK」から「JTAG Clock」に変更します。

これによりJTAGによるコンフィグレーションが可能になります。

「OK」でプロパティ画面を終了します。

これで全ての設定が完了です。