亙僇儊儗僆儞USB SPA3傾僾儕働乕僔儑儞偺峔惉亜

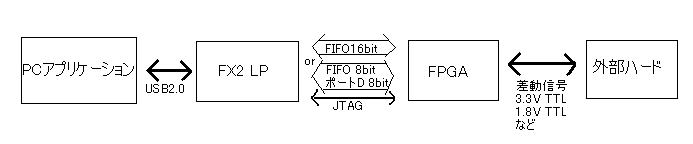

傾僾儕働乕僔儑儞慡懱偺峔惉偼壓婰偺恾偺傛偆偵側傝傑偡丅

FX2偲FPGA偺娫偺捠怣偼丄乽FIFO 16bit乿偁傞偄偼乽FIFO 8bit + 億乕僩8bit乿傪慖戰偟傑偡丅

JTAG偼FPGA偺僐儞僼傿僌儗乕僔儑儞偵巊梡偟傑偡偑丄僐儞僼傿僌儗乕僔儑儞廔椆屻偼傾僾儕働乕僔儑儞偺僨乕僞揮憲偵巊梡弌棃傑偡丅

傾僾儕働乕僔儑儞慡懱偱尒傞偲奐敪偟側偔偰偼側傜側偄偺偼

偺3偮偑昁梫偵側傝傑偡丅

FX2偺CPU偱偁傞8051偼8bit偱丄摦嶌僋儘僢僋傕48MHz偲昻庛偱偡丅偙偺偨傔丄幚嵺偺僨乕僞乕張棟偼PC懁偱峴偆偙偲偵側傝傑偡丅

FX2偑張棟偟側偔偰偼側傜側偄偺偼丄USB偺惂屼丄FPGA偺僐儞僼傿僌儗乕僔儑儞丄JTAG傪巊梡偟偨FPGA偲偺捠怣偱偡丅

偙偺傛偆側張棟偼丄偳偺傾僾儕働乕僔儑儞偱傕昁梫側晹暘偱偡偺偱丄屄暿偵奐敪偟側偄偱嵪傑偣偨偄晹暘偱偡丅

偦偙偱崱夞丄Spartan3A偵摿壔偟偨FX2梡偺僼傽乕儉僂僄傾傪奐敪偟傑偟偨丅

偙傟偵傛傝丄傾僾儕働乕僔儑儞奐敪幰偼FX2偺僪僉儏儊儞僩傪撉傫偩傝丄FX2梡偺僼傽乕儉僂僄傾偺奐敪偐傜夝曻偝傟傑偡丅

傑偨丄PC傾僾儕働乕僔儑儞偐傜尒傟偽丄FPGA偵懳偟偰崅懍偵僨乕僞偺庴偗搉偟傪峴偆偙偲偑廳梫偱偡丅

FX2傪巊梡偟偰崅懍偵僨乕僞揮憲傪峴偆偵偼丄Cypress偺採嫙偡傞CyAPI儔僀僽儔儕傪巊梡偟偰丄USB偺摨婜揮憲傪峴偄傑偡丅

摨婜揮憲偼旕摨婜揮憲偲斾傋偰丄埖偄偑柺搢側偺偱偡偑丄僆僾僥傿儅僀僘偺採嫙偡儔僀僽儔儕傪巊梡偡傞偙偲偱丄娙扨偵埖偆偙偲偑壜擻偵側傝傑偡丅

亙SPA3儔僀僽儔儕偺峔惉亜

僇儊儗僆儞USB SPA3儔僀僽儔儕偺峔惉偼壓婰偺恾偺傛偆偵側偭偰偄傑偡丅

SPA3僋儔僗偺娭悢傪巊梡偡傞偙偲偱丄FX2 FW偺儘乕僪丄FPGA僐儞僼傿僌丄FIFO/僄儞僪億僀儞僩惂屼丄JTAG宱桼偱偺僽儘僢僋RAM/億乕僩傾僋僙僗傪峴偆偙偲偑弌棃傑偡丅

嬶懱揑側巊梡曽朄偼丄僒儞僾儖傗僜乕僗僐乕僪傪嶲徠偟偰偔偩偝偄丅

| PC傾僾儕働乕僔儑儞 | |||||||

| FIFO傪巊偭偨 崅懍摨婜揮憲 |

JTAG RAM傾僋僙僗 |

JTAG 億乕僩 |

FPGA 僐儞僼傿僌 |

FX2 FW 儘乕僪 |

FIFO 惂屼 |

億乕僩D 惂屼 |

僄儞僪億僀儞僩 惂屼 |

| SPA3僋儔僗 | |||||||

| CyUSB僐儞僩儘乕儖 | |||||||

| CUSB2僋儔僗 | |||||||

亙SPA3儔僀僽儔儕偺娭悢亜

| 暘椶 | 娭悢 | 摦嶌 |

| 弶婜壔 FPGA僐儞僼傿僌 |

bool init(cusb2 *usb, u64 *dev_dna, u8 *bit_buf) | dev_dna偱巜掕偟偨僇儊SPA3偵FW傪儘乕僪偟偰弶婜壔偡傞丅 dev_dna偑僛儘偺応崌偼丄嵟弶偵尒偮偐偭偨僇儊SPA3傪僞乕僎僢僩偵偡傞丅 bit_buf偵偼ISE偱嶌惉偟偨僐儞僼傿僌梡僀儊乕僕傪巜掕偡傞丅 婛偵FPGA偑僐儞僼傿僌嵪傒偺応崌偼丄FPGA撪晹偺bit僀儊乕僕偺僞僀儉僗僞儞僾偲斾妑偟偰丄堎側傟偽儕僐儞僼傿僌傪峴偆丅 |

| JTAG I/O億乕僩 |

void port(u8 bits, u8 *out, u8 *in) | JTAG捠怣傪峴偄丄FPGA撪晹偵峔抸偟偨I/O億乕僩偵傾僋僙僗偡傞丅 bits偼億乕僩偺憤價僢僩悢乮IN/OUT億乕僩偺戝偒偄曽乯丄 out偼弌椡億乕僩偺價僢僩僀儊乕僕傪僙僢僩偡傞丅 in偵偼擖椡億乕僩偺忬懺偑栠傝抣偲偟偰僙僢僩偝傟傞丅 |

| JTAG RAM傾僋僙僗 |

void mem_read(u16 addr, u16 word, u16 *buf) | JTAG捠怣傪峴偄丄FPGA撪晹偺僽儘僢僋RAM傪撉傒弌偡丅 傾僪儗僗(addr)偼13bit桳岠偱丄word偼撉傒弌偡儚乕僪悢(16bit)傪巜掕偡傞丅撉傒弌偟偨撪梕偼buf偵奿擺偝傟傞丅 |

| void mem_write(u16 addr, u16 word, u16 *buf) | JTAG捠怣傪峴偄丄FPGA撪晹偺僽儘僢僋RAM偵彂偒崬傓丅 傾僪儗僗(addr)偼13bit桳岠偱丄word偼彂偒崬傓儚乕僪悢(16bit)傪巜掕偡傞丅彂偒崬傓撪梕偼buf偵奿擺偟偰偍偔丅 |

|

| 僄儞僪億僀儞僩 惂屼 |

void ep6in_start() | 僇儊SPA3 -> PC 傊偺揮憲傪奐巒偡傞丅 |

| void ep6in_stop() | 僇儊SPA3 -> PC 傊偺揮憲傪掆巭偡傞丅 | |

| void ep2out_start | PC -> 僇儊SPA3 傊偺揮憲傪奐巒偡傞丅 | |

| void ep2out_stop() | PC -> 僇儊SPA3 傊偺揮憲傪掆巭偡傞丅 | |

| 億乕僩D惂屼 | void portd_cfg(u8 dir) | 億乕僩D偺奺bit偺擖椡丒弌椡傪愝掕偡傞丅(0:擖椡 1:弌椡乯 |

| u8 portd_read() | 億乕僩D傪撉傒弌偡丅 | |

| void portd_write(u8 val) | 億乕僩D偵彂偒崬傓丅 | |

| FIFO惂屼 | void ifconfig(u8 val) | FIFO偺摦嶌儌乕僪丄僋儘僢僋側偳傪愝掕偡傞丅 僒儞僾儖僐乕僪丄FX2僨乕僞乕僔乕僩嶲徠丅 |

| void set_fifo_8() | FIFO傪8bit儌乕僪偵愝掕偡傞丅 | |

| void set_fifo_16() | FIFO傪16bit儌乕僪偵愝掕偡傞丅 |

亙SPA3 FX2 FW亜

SPA3儔僀僽儔儕偼FX2偵儘乕僪偝傟偨FW乮僼傽乕儉僂僄傾乯傪巊梡偟偰丄Spartan3A傪惂屼偟傑偡丅

摨帪偵偙偺FW偼USB偵娭偡傞張棟傕峴偭偰偄傑偡丅

暋悢偺僇儊儗僆儞USB SPA3偑PC偵愙懕偝傟偨嵺偵丄偳偺傛偆側曽朄偱屄乆偺僇儊儗僆儞USB

SPA3傪幆暿偡傞偐偼廳梫側栤戣偱偡丅

摿偵丄僇儊儗僆儞USB SPA3偼PC偐傜僟僀僫儈僢僋偵僐儞僼傿僌儗乕僔儑儞傪峴偄傑偡偺偱丄堄恾偟側偄僇儊儗僆儞USB

SPA3偵懳偟偰丄僐儞僼傿僌儗乕僔儑儞傪峴偭偰偟傑偆偲丄Spartan3A僨僶僀僗偺攋懝偺壜擻惈傕偁傝傑偡丅

偟偐偟側偑傜丄僇儊儗僆儞USB SPA3偺FX2偵偼EEPROM偑幚憰偝傟偰偄傑偣傫丅偙偺偨傔乽僇儊儗僆儞USB

FX2乿偱巊梡偟偨傛偆側丄EEPROM偵ID傪彂偒崬傫偱偍偔偲偄偭偨庤朄偼巊偊傑偣傫丅

偦偙偱Spartan3A偵彂偒崬傑傟偰偄傞屌桳偺ID偱偁傞Device DNA僐乕僪傪巊梡偟傑偡丅FX2

FW偼FX2偱幚峴偝傟傞偲丄傑偢Spartan3A偐傜Device DNA傪撉傒弌偟傑偡丅偦偟偰丄Device

DNA傪USB僨僶僀僗偺僔儕傾儖僫儞僶乕偲偟偰巊梡偟偰丄嵞搙擣幆乮儕僫儉儗乕僔儑儞乯偝傟傑偡丅僔儕傾儖僫儞僶乕偲偼USB偺儀儞僟乕ID傗僾儘僟僋僩ID偲摨條偵丄USB偺婯奿偺拞偱掕傔傜傟偰偄傑偡丅

PC傾僾儕働乕僔儑儞偱偼丄Device DNA斣崋傪巜掕偡傞偙偲偱丄摿掕偺僇儊儗僆儞USB

SPA3傪幆暿偡傞偙偲偑弌棃傑偡丅Device DNA斣崋偵僛儘傪巜掕偡傞偲丄嵟弶偵尒偮偗偨僇儊儗僆儞USB

SPA3傪懳徾偵偡傞偙偲偑弌棃傑偡丅

僆僾僥傿儅僀僘偺暿偺惢昳乽僇儊儗僆儞USB FX2乿偼FX2偲傾儖僥儔偺CPLD MAX2傪幚憰偟偨丄僇儊儗僆儞USB

SPA3偲峔惉偑帡偰偄傑偡丅偙偺偨傔丄乽僇儊儗僆儞USB FX2乿偲乽僇儊儗僆儞USB

SPA3乿偑崿嵼偟偨忬懺偱傕丄幆暿偺栤戣偑敪惗偟傑偡丅

乽僇儊儗僆儞USB FX2乿偼慜弎偺捠傝丄EEPROM偵ID傪彂偒崬傓偙偲偱幆暿偟傑偡偑丄乽僇儊儗僆儞USB

SPA3乿傕ID 僛儘斣偲偟偰埖傢傟偰偟傑偄傑偡丅偱偡偐傜丄乽僇儊儗僆儞USB FX2乿偲乽僇儊儗僆儞USB

SPA3乿偑崿嵼偡傞娐嫬偱偼丄昁偢乽僇儊儗僆儞USB FX2乿偵僛儘斣埲奜偺ID傪彂偒崬傫偱巊梡偟偰偔偩偝偄丅

亙僒儞僾儖丂I/O億乕僩仌Device DNA偵傛傞僙僉儏儕僥傿亜

幚嵺偵SPA3儔僀僽儔儕傪巊梡偡傞娙扨側僐儞僜乕儖傾僾儕働乕僔儑儞傪嶌偭偰傒傑偡丅

偙偺僒儞僾儖偱偼USB偺崅懍揮憲偵偮偄偰偼丄堦愗峴偄傑偣傫丅USB偺崅懍揮憲偵偮偄偰偼丄USB懍搙應掕僣乕儖傪嶲徠偔偩偝偄丅

僇儊儗僆儞USB SPA3偱偼Device DNA傪幆暿偺偨傔偵巊梡偟偰偄傑偡偑丄杮棃Device

DNA偼FPGA儘僕僢僋偺僙僉儏儕僥傿乕乮僐僺乕杊巭乯偺偨傔偵巊梡偝傟傑偡丅

Device DNA偼儐僯乕僋側抣偱偡偺偱丄FPGA撪晹偱DNA偐傜僉乕傪惗惉偝偣傑偡丅僉乕傪惗惉偡傞傾儖僑儕僘儉偼FPGA撪晹偵偁傝傑偡偺偱丄娙扨偵夝愅偡傞偙偲偼弌棃傑偣傫丅偦偟偰PC傾僾儕働乕僔儑儞偐傜偼丄DNA偵懳墳偡傞擣徹僐乕僪傪FPGA偵彂偒崬傒傑偡丅擣徹僐乕僪偼傾僾儕働乕僔儑儞奐敪幰偑FPGA撪晹偲摨偠傾儖僑儕僘儉偱惗惉偟傑偡丅FPGA撪晹偱偼丄彂偒崬傑傟偨擣徹僐乕僪偲僉乕傪斾妑偟偰丄堦抳偟側偄応崌偼婡擻傪惂尷偝偣傑偡丅PC偺傾僾儕働乕僔儑儞傪偄偔傜夝愅傗僋儔僢僉儞僌傪偟偨偲偙傠偱丄FPGA撪晹偺僙僉儏儕僥傿乕傪撍攋偡傞偙偲偼弌棃傑偣傫偺偱丄偐側傝嫮屌側僙僉儏儕僥傿乕傪峔抸偱偒傑偡丅

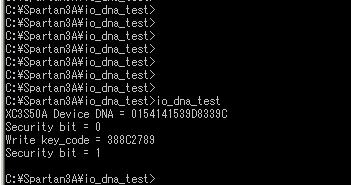

崱夞偺僒儞僾儖偱偼丄FPGA儘僕僢僋撪晹偱撉傒弌偟偨DNA傪JTAG擖椡億乕僩傪夘偟偰丄PC偑撉傒庢傝丄擣徹僐乕僪傪惗惉偟偰丄JTAG弌椡億乕僩傪夘偟偰FPGA偵彂偒崬傒傑偡丅偦偺屻JTAG擖椡億乕僩傪夘偟偰丄FPGA撪晹偺擣徹寢壥傪撉傒弌偟傑偡丅

僜乕僗僐乕僪仌僶僀僫儕堦幃(io_dna_test.zip)僟僂儞儘乕僪

張棟撪梕偼扨弮偱

PC傾僾儕働乕僔儑儞偺僜乕僗僐乕僪偺夝愢偱偡丅

| Visual C++ 2010 Express 僜乕僗僐乕僪 |

|

| 3峴栚偼丄FPGA偺僨僓僀儞傪奐敪拞偼僐儊儞僩傾僂僩偟傑偡丅 ISE偑惗惉偟偨bit僼傽僀儖傪僟僀儗僋僩偵斀塮偝偣丄儘僕僢僋偺僨僶僢僌偑壜擻偱偡丅 FPGA偺僨僓僀儞奐敪偑廔椆偟偨傜丄"spa3_bit.inc"僼傽僀儖偵庢傝崬傒丄僾儘僌儔儉偵撪憼偝偣傑偡丅 |

|

| cusb2丄spa3僋儔僗偼僾儘僌儔儉慡懱偱丄傾僋僙僗弌棃傞偲曋棙側偺偱丄僌儘乕僶儖億僀儞僞偱愰尵偟傑偡丅乮崱夞偺僒儞僾儖偱偼柍堄枴偱偡乯 |

|

| 1峴栚偱億乕僩偺價僢僩悢傪掕媊偟偰偄傑偡丅偙偺掕媊偼屻偺port()娭悢偱巊梡偟傑偡丅FPGA偺僨僓僀儞偲偙偺抣偑堦抳偟偰偄傞昁梫偑偁傝傑偡丅 3-5峴栚偱弌椡億乕僩(PC -> FPGA)偺掕媊傪峴偄傑偡丅C尵岅偺價僢僩僼傿乕儖僪傪巊偭偰掕媊偟傑偡丅偙偺傛偆偵偡傞偙偲偱丄億乕僩傪曄悢偺傛偆偵埖偆偙偲偑弌棃傑偡丅 7-10峴栚偼擖椡億乕僩(FPGA -> PC)偺掕媊偱偡丅崌寁偱58bit偱偡丅弌椡億乕僩偼32bit偱偟偨偺偱丄崱夞偺僒儞僾儖偱偼擖椡億乕僩偺曽偑價僢僩悢偑懡偄偙偲偵側傝傑偡丅價僢僩悢偺懡偄曽傪丄1峴栚偺掕媊偵巊梡偟傑偡丅 |

|

| main娭悢偱偡丅3-8峴栚偼僨僶僢僌拞偺bit僼傽僀儖乮儘僕僢僋乯傪撉傒崬傓張棟偱偡丅 |

|

| 1峴栚偼Device DNA偺曄悢掕媊偱偡丅Device DNA偼57bit偱偡偺偱丄u64傪巊梡偟傑偡丅 2亅3峴栚偱cusb2偲spa3傪幚懱壔偟偰偄傑偡丅 |

|

| 1峴栚偱dev_dna偵僛儘傪擖傟傞偙偲偱丄嵟弶偵尒偮偗偨僇儊SPA3傪僞乕僎僢僩偵偟傑偡丅尒偮偐偭偨SPA3偺Device

DNA偺抣偑dev_dna偵栠傝傑偡丅摿掕偺Device DNA傪僞乕僎僢僩偵偡傞応崌偼丄偦偺抣傪dev_dna偵戙擖偟偰屇傃弌偟傑偡丅 2峴栚偱丄巜掕偟偨僞乕僎僢僩偺FX2偵FW傪儘乕僪偟偰丄FPGA偺僐儞僼傿僌儗乕僔儑儞傪峴偄傑偡丅惓忢廔椆偡傞偲True偑曉傝傑偡丅 |

|

| 1峴栚偱弌椡億乕僩偺key_code偵戙擖偟偰偄傑偡丅掕媊偟偨曄悢偵戙擖偡傞偙偲偱丄愝掕偡傋偒抣偑峔憿懱偵僙僢僩偝傟傑偡丅 2峴栚偱僙僢僩偟偨峔憿懱傪丄port()娭悢偱FX2->FPGA偵憲怣偟傑偡丅摨帪偵擖椡億乕僩偺抣偑in_port峔憿懱偵僙僢僩偝傟偰丄栠偭偰偒傑偡丅 3亅4峴栚偼in_port偵僙僢僩偝傟偰栠偭偰偒偨擖椡億乕僩偺抣傪昞帵偟傑偡丅 |

|

| FPGA偐傜撉傒弌偟偨Device DNA傪尦偵丄擣徹僐乕僪傪惗惉偟偰偄傑偡丅杮棃偙偺張棟偼傾僾儕働乕僔儑儞採嫙幰偑峴偄丄傾僾儕働乕僔儑儞僾儘僌儔儉偵傾儖僑儕僘儉偑慻傒崬傑傟傞偙偲偼偁傝傑偣傫丅 |

|

| 1峴栚偱key_code傪FPGA偵憲怣偟傑偡丅in_port偵抣偑栠傝傑偡偑丄偙偺抣偼key_code傪彂偒崬傓慜偺忬懺偱偡丅 2峴栚偱key_code偑斀塮偝傟偨忬懺偺in_port傪庢摼偟傑偡丅 3峴栚偱FPGA偑曉偟偨僙僉儏儕僥傿忬懺傪昞帵偟傑偡丅 |

|

| 1亅3峴栚丂師夞偺偨傔偵晄惓側僉乕傪彂偒崬傫偱偍偔 |

懕偄偰丄FPGA偺儘僕僢僋晹暘偺僜乕僗僐乕僪偱偡丅Verilog偱婰弎偟偰偄傑偡丅

| XILINX ISE Verilog 僜乕僗僐乕僪乮io_dna.v乯 |

|

| 僩僢僾儌僕儏乕儖偺掕媊偱偡丅僇儊SPA3偼FX2偲愙懕偝傟偰偄傑偡偺偱丄巊梡偟側偄怣崋傕巆偟偰偍偒傑偡丅摨帪偵ucf僼傽僀儖偱僺儞斣崋傕屌掕偡傞昁梫偑偁傝傑偡丅徻偟偔偼偙偪傜傕嶲徠丅 |

|

| 弌椡怣崋偼枹巊梡偩偲ISE偺僄儔乕偵側傞偺偱丄揔摉偵愝掕偟偰偍偔丅 |

|

| 擖弌椡億乕僩偺怣崋柤傪掕媊丅幚懱偼壓婰偺jtag_port撪晹偱掕媊偝傟傞丅58bit偼壓婰偺丄僀儞僗僞儞僗壔偲PC傾僾儕偲堦抳偡傞昁梫偑偁傝傑偡丅 |

|

| jtag_port傪僀儞僗僞儞僗壔偟傑偡丅jtag_port偼jtag_port.v偵婰弎偝傟偰偄傑偡丅價僢僩悢偼壜曄偵側偭偰偄傑偡偺偱丄擖弌椡億乕僩偺戝偒偄曽傪愝掕偟傑偡丅jtag_port撪晹偱偼丄58*2屄偺儗僕僗僞偑掕媊偝傟巊梡偝傟傑偡丅 崱夞偼JTAG RAM傾僋僙僗傪巊梡偟傑偣傫偑丄JTAG RAM傾僋僙僗傪巊梡偡傞応崌偼丄spd_chk16偺僒儞僾儖偵娷傑傟傞jtag_port.v傪巊梡偟偰偔偩偝偄丅 |

|

| Device DNA傪撉傒弌偡儌僕儏乕儖(dna.v)傪僀儞僗僞儞僗壔丅Device DNA偺撉傒弌偟偼僔儕傾儖偵峴傢傟傞偨傔丄FX2偐傜忢帪弌椡偝傟傞12MHz偺僋儘僢僋傪巊梡偟偨丅 |

|

| 2亅3峴栚偵拲栚偟偰偔偩偝偄丅怣崋key_code傪掕媊偟偰丄偙傟傪out_port偵傾僒僀儞偟傑偡丅偙偺婰弎偵傛偭偰丄PC -> FPGA傊偺弌椡億乕僩偑key_code偲偟偰寢傃偮偗傜傟傑偡丅 |

|

| Device DNA偐傜僉乕傪惗惉偟丄PC偐傜彂偒崬傑傟偨抣偲斾妑偟傑偡丅斾妑寢壥傪security怣崋偵戙擖偟傑偡丅 |

|

| 偙偺峴傕廳梫偱偡丅FPGA -> PC傊偺擖椡億乕僩(in_port乯傪security偲dev_dna偵妱傝摉偰傑偡丅偙偺妱傝摉偰偼丄PC懁偺傾僾儕働乕僔儑儞偱偼峔憿懱偺價僢僩僼傿乕儖僪偲偟偰掕媊偟偰巊梡偝傟傑偡丅 |

|