キットが届きましたら部品を確認してください。

基板のRev.が2.0以前の方はこちら

<回路図>

回路図 Rev2.0(PDF)

Rev1.1からの変更点はこちらを参照ください

<コンフィグROM(XCF02) 新リビジョンコード対応>

2006.08.30版では、新しいrevisionコードを持つXCF02Sを認識しない不具合が修正されました。

旧バージョンのezfc.exeでコンフィグROMの消去・書き込みが出来ない場合は新バージョンとなります。

今後、新しいロットのezfpgaで基板上のコンフィグROMを使用される場合には、

下記手順にて、ezfpgaライブラリを2006.08.30版に更新してください。

1.ダイナミックライブラリ(ezfpga.dll)を使用している場合

ezfpga.dllを最新版のファイルに置き換えます。

ユーザープログラムはそのままで使用できます。

2.スタティックライブラリ(ezfpga.a、ezfpga.lib)を使用している場合

ezfpga.a又はezfpga.libを最新版に置き換えて再リンクを行って下さい。

ソースコードの変更は不要です。

3.ezfc.exeツールをVer1.02の最新版を使用する

コンフィグROMを使用していない場合や、旧ロットに限定して使用される

ケースでは、必ずしもライブラリを更新する必要はありません。

ダウンロード

<製作>

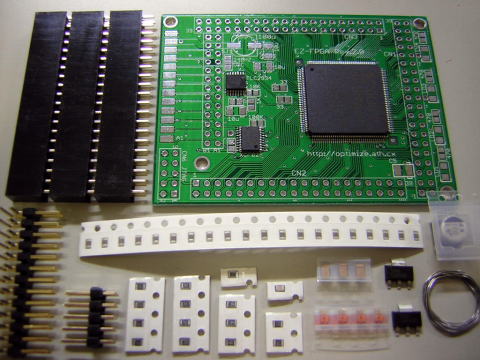

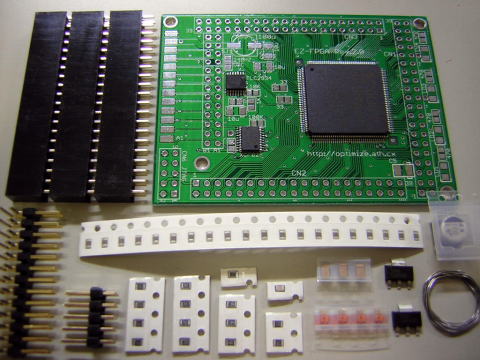

キットが届きましたら部品を確認してください。

| 部品 | 数 | 備考 |

| 専用プリント基板 | 1 | XC2S100-5TQ144C、TLC2934、XCF02実装済み |

| 電解コンデンサ 100uF/16V | 1 | 極性あり |

| タンタルコンデンサ 10uF/10V | 3 | 極性あり |

| チップ抵抗 470Ω | 4 | 471 |

| チップ抵抗 1KΩ | 4 | 102 |

| チップ抵抗 10KΩ | 1 | 103 |

| チップ抵抗 33Ω | 2 | 330 |

| チップ抵抗100KΩ | 3 | 104 |

| チップコンデンサ 22pF | 1 | |

| チップコンデンサ 0.1uF | 19+1 | 1個は予備 |

| 3.3Vレギュレータ | 1 | IRU-1206-33 |

| 2.5Vレギュレータ | 1 | IRU-1206-25 |

| チップLED 赤 or 緑 | 4 | 極性あり(緑がカソード) |

| L字ピンヘッダ 2*13 | 1 | |

| ピンヘッダ 2*5 | 1 | |

| ピンフレーム 2*20 | 3 | |

| 糸はんだ | 1 |

20-30W程度の先端の細い半田ごて、ピンセット、ルーペ(虫眼鏡)、はんだを用意してください。

チップ部品のはんだ付けは、片側のランドにはんだを盛っておき、半田ごてではんだを溶かしながら、ピンセットでチップ部品を固定します。

ピンセットでチップ部品を飛ばしたりしないように注意してください。

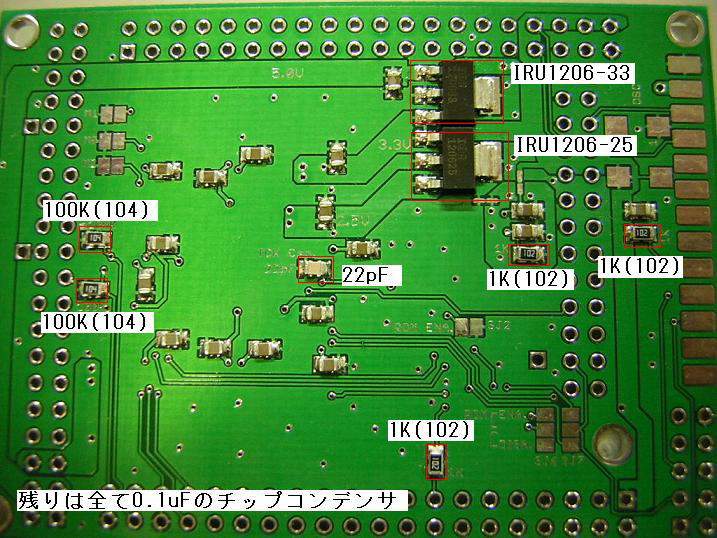

1) 基板の裏面からはんだ付けを行います

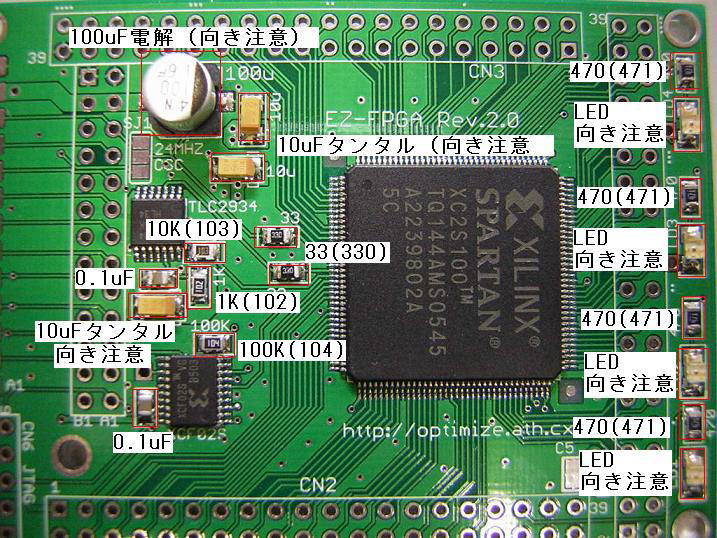

2) 次に表面

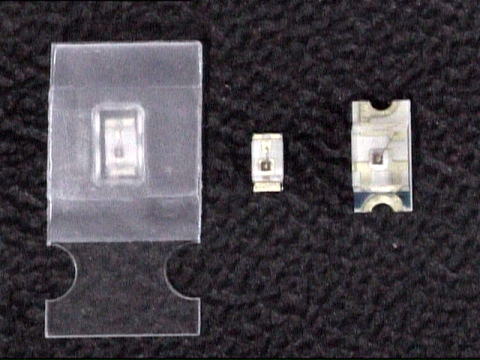

チップLEDは極性がありますご注意ください。下の写真のように下がカソード(緑)になるように取り付けます。

チップLEDは上記サイズ(2012サイズ)のものが入手困難のため、

下記写真中央の小型(1608サイズ)になる場合があります。

取り付けの向きは、写真と同じ向きになります。(LEDレンズ内の四角が下にくる向き)

テーピング(包装)されている状態では、下側にスプロケット(穴)がくる向きです。

(上記写真のLEDは全て下側がカソードです)

半田付けは上記写真のように、中央に取り付けて、各々のランドと接触するようにします。

3) コネクタ接続方法の決定&取り付け

(説明に使用している写真はRev1の基板ですが、Rev2でも同様です)

EZ-FPGA Rev2はMINI EZ-USBを接続してFPGAのコンフィグや、コンフィグ用ROMへの書き込みなどを行うことが出来ます。MINI EZ-USB以外にもXILINX準拠のパラレルケーブルをJTAGコネクタ(CN6)に接続して使用することも出来ます。使用するコンフィグ方法のコネクタを取り付けます。

XILINXのParallel Cable IIIを使用してコンフィグを行う。 抵抗3本とコンデンサ1個で作成した

XILINX互換簡易パラレルケーブル詳しくはこちら電源はCN4にUSB-Bコネクタを付けてUSBから5Vを供給している

MINI EZ-USBを接続するとUSB経由でコンフィグが出来る

電源もUSBのバスパワーから取得するのですっきり

MINI EZ-USBの接続方法もCN4にL字ピンヘッダを使用して接続する方法と、エッジにストレートピンヘッドを付けて接続する方法の2種類があります。

L字ピンヘッダ(キットに付属)

メリット ピンヘッダが基板の外にはみ出ないため取り回しが楽 デメリット CN4をつぶしてしまうためEZ-USBのデータバスをFPGAに接続する場合EZ-FPGA基板の裏でジャンパする必要あり JTAGコネクタにリボンケーブルを接続するとL字ピンヘッダのピンが邪魔して深く刺さらない

(一応接触していますので動きますが、、)

リボンケーブルではなく普通のピンフレームなら問題ありませんストレートピンヘッダ

メリット CN4がつぶれないのでコネクタを取り付けることで、外部でEZ-USBのデータバスをFPGAに接続することが出来る

デメリット ピンヘッダが基板の外にはみ出るので邪魔 結合度はL字ピンヘッダより弱い

4) ソルダジャンパ(SJ)の設定

EZ-FPGA Rev2はコンフィグROMを搭載しています。Rev1と比べると基板上のスペースが限られ、更にコンフィグROMの有効/無効のためのジャンパが増えました。

このため、Rev1で使用していたジャンパピンに替わってソルダジャンパ(SJ)を採用しています。ソルダジャンパは半田を基板上のパッドに盛ることでON/OFFを行います。(ソルダジャンパ一覧表(Excel))

<SJ1 クロック切り替えジャンパ>

FPGAのGCK3に入力するクロックをEZ-USBが供給する24MHzか、OSC(FXO-31FL)にするか選択します。

ここでは24MHz側に半田を盛って、EZ-USBの24MHzを使用する設定にします。(推奨)

FXO-31FLを使用する場合は下側に半田を盛ります。

FXO-31FL(37FL)はフルタカパーツセンターのWEB通販で希望周波数のものを入手できます。

Rev1基板で使用可能であった、DIPパッケージのOSC(EXO-3)はRev2では基板スペースの関係で使用できません。

<SJ2、SJ6、SJ7 コンフィグROM関連ジャンパ>

コンフィグROMはFPGAの後ろにデイジーチェイン接続され、EZ-USBやJTAGケーブルなどを使用して書き込むことが可能です。

コンフィグROMが搭載されているのはRev2基板からですので、従来のRev1用に作成されたアプリケーションを動かすためには、コンフィグROMを無効にして、デイジーチェイン接続を解除(FPGAをJTAG直結にする)必要があります。

SJ2 オープン コンフィグROM無効 クローズ コンフィグROM有効 SJ6

SJ71-2クローズ デイジーチェイン有効

(コンフィグROM有効)2-3クローズ デイジーチェイン無効

(コンフィグROM無効)

コンフィグROM無効

(Rev1互換)コンフィグROM有効

(推奨)SJ2:オープン

SJ6/SJ7:2-3クローズSJ2:クローズ

SJ6/SJ7:1-2クローズ

コンフィグROMが有効(デイジーチェイン接続が有効)な状態では、PC<->FPGA間の通信速度が低下します。

このため、高速なJTAG通信が必要なアプリケーションの場合はデイジーチェイン接続を無効にすると効果的です。

<SJ3、SJ4、SJ5 コンフィグモード(M1/M0/M2)切替ジャンパ>

FPGAのコンフィグモード設定用のジャンパです。詳しくはSpartan2のデーターシートや、EZ-FPGAライブラリのドキュメントを参照してください。

Rev1基板の場合はデフォルトで全てオープンになっていますので、Rev1との互換性を重視する場合は全てオープンで使用します。

コンフィグROMからのセルフコンフィグを行うためには、マスターシリアルモードに設定する必要があります。マスターシリアルモードに設定した状態でも、コンフィグROMが消去された状態であれば、EZ-USBやJTAGからFPGAのコンフィグを行うことが可能です。通常の使用においてはこの状態を推奨します。

Rev1互換 コンフィグROM有効(セルフコンフィグ)

(推奨)SJ2:オープン

SJ3:オープン

SJ4:オープン

スレーブシリアル プレプルアップ無しSJ2:クローズ

SJ3:クローズ

SJ4:オープン

マスターシリアル プレプルアップ有り

これ以降の手順はコンフィグROMを有効にした状態で、MINI EZ-USBを使用して動作確認を行う手順です。コンフィグROMを無効にしている場合や、MINI EZ-USB以外を使用した場合は手順が異なります。

5)動作チェック(FPGA/PLL)

(EZ-USBのデバイスドライバのインストールされていて、MINI EZ-USBが正常動作(旧型の場合はCLKのジャンパも忘れずに)することが前提です。詳しくはMINI EZ-USBのページをご確認ください。)

40ピンコネクターを取り付ける前に、FPGAの動作チェック、PLLの動作チェック、FPGAの半田不良チェック、コンフィグROMの書き込みテストを行います。ICは自動マウンター&リフローで実装を行っていますので、半田不良はまず無いと思われますが、40ピンコネクターを取り付けてしまうと半田のリワークが難しくなりますのでこの段階で確認しておきます。

まず電源を入れる前に各電源ライン(GND、+5V、+3.3V、+2.5V)同士がショートしていないかをテスターで調べます。

(3.3Vと2.5Vの間のパターンがGNDです)

ショートしていないことが確認できたらMINI EZ-USBを接続し、PCと接続してください。

チップLEDのLD1とLD2が点燈するはずです。

念のため3.3Vと2.5Vの電圧をテスターで測っておいてください。

問題なければezftest2.exe(ダウンロード)を実行してください。

FPGAのコンフィグレーションが終了するとLD1が消燈します。

ezftestは

・I/OとGNDのショートチェック

・I/OとVCCのショートチェック

・I/Oピン同士のショートチェック

・X'tal OSC、VCO発振チェック

・PLLのロック確認

を行います。

PLL、FPGAチップは基板に半田実装済みですが、ごくまれに半田不良や基板不良があるようです。この時点で確実にチェックしておくことが重要です。

ezftest2はパラレルケーブルでも使用できます。起動方法は"ezftest 378"のようにパラレルポートのI/Oアドレスを指定します。パラレルポートで使用するためにはOSにgiveio.sysを組み込むか、同一ディレクトリにgiveio.sysをおいておく必要があります。実行にはアドミニ権限が必要です。

パラレルケーブrを使用する場合は、GCK3に10MHz以上のクロックが必要です。

EZ-FPGA基板上にオシレータを実装してください。

下記のように表示されればOKです。

(エラーがある場合はErrorの表示ととも該当個所が色で表示されます。)

ESCキーを押してezftest2.exeを終了して、USBケーブルを抜いてください。

I/Oのショート関係は自動的にチェックされますが、実際にFPGAのI/Oがコネクタまで結線されているかを確認します。

LD3とLD4のLEDはユーザが自由に使用できるようになっていますので、テスト用のプローブを作成します。

適当な配線材(キットには含まれませんので手持ちのものを使用)をLD3かLD4に半田付けします。

USBケーブルを接続して再度ezftest2.exeを起動しします。

配線材の反対側をCN1-CN3の各ピンに接触させていきます。LEDはI/Oピンでは点滅し、GNDピンでは点燈します。

(CN2-33をチェックする際に、CN2-15もSENSE H表示になりますが、これは問題ありません)

順次テストしていくとテスト済みのI/OピンはOKの色(グリーン)に変化していきますので、全てのI/Oピンをテストします。

6)コンフィグROM動作確認(セルフコンフィグ)

コンフィグROMに動作確認用のデザインを書き込んで、ROMからコンフィグが行えることを確認します。

ezfled_060215.lzhをダウンロードして解凍します。

USBケーブルをPCと接続し、解凍して出来たezfled.ezfファイルをezfc.exeにドラッグ&ドロップします。ezfled.ezfファイルはスクリプトファイルで、ROMをイレースした後に、デザインファイルezfled.bitを書き込みます。

このように表示されればOKです。

USBケーブルをPCから抜き、再度挿入します。

LD1(DONE)が消燈すれば、セルフコンフィグ成功です。ezftest2と同様にI/OピンとLD3あるいはLD4を接続するとLEDが点滅するのが確認できます。

セルフコンフィグが確認できましたので、コンフィグROMを消去します。

(消去しておかないと、EZ-USBなどのJTAGデバイスによるコンフィグが出来なくなります。)

消去するには、xerase.ezfファイルをezfc.exeにドラッグ&ドロップします。

このような画面が表示されればOKです。

今度はUSBケーブルの抜き差し(電源OFF/ON)を行ってもLD1(DONE)は消燈しないはずです。

7)コネクタの半田付け

残りの2*20ピンフレームコネクタを半田付けします。

EZ-FPGAはマザーボードとして使用することを想定していますが、CN1-3を下向きに取り付けることで、他の基板のアドオンボードとしても使用できます。

マザーボード アドオンボード

JTAGによるコンフィグを行う場合は2*5のピンヘッダも半田付けします。

これで完成です。