<MAX2のサンプルデザインを作成する>

Quartus2を使用して、MAX2のサンプルデザインを作成してみることにします。

今回はVerilogを使用していますが、VHDLでも同様に作成することが出来ます。

サンプルデザインの定番と言えばLED点滅です。今回もこのLED点滅を作ってみることにします。

発振器のクロックをカウンターでカウントすることでLEDの点滅を作り出すことが出来ます。

FPGA/CPLDの場合は通常外部に発振器を使用するのですが、今回はMAX2に内蔵されているRCオシレータを使用することにします。

RCオシレータはMAX2が自分自身のコンフィグレーション(MAX2はCPLDでありながら、FPGAのようなSRAM構成です)を行うために実装されているのですが、ユーザのデザインにも使用することが出来ます。

RCオシレータですので正確な周波数は期待できませんが、3.3MHz〜5.5MHzの間で発振します。

このRCオシレータを使うことで、外付け部品なしでMAX2をシーケンサーとして動作させることなども可能になります。

<プロジェクトの作成>

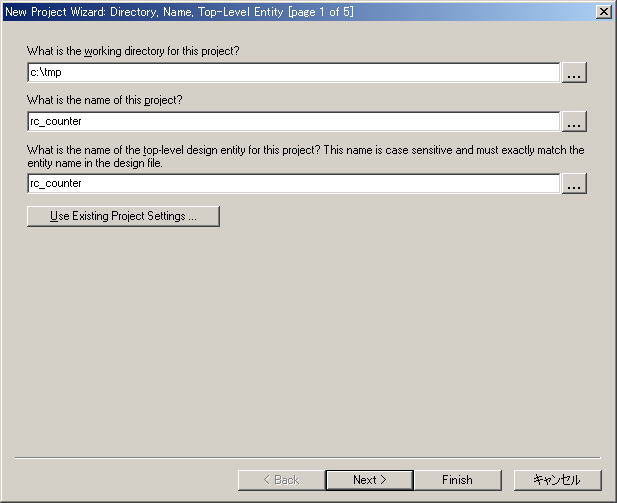

Quartus2ではデザインをプロジェクトとして管理します。ですので、まずはプロジェクトを作成します。

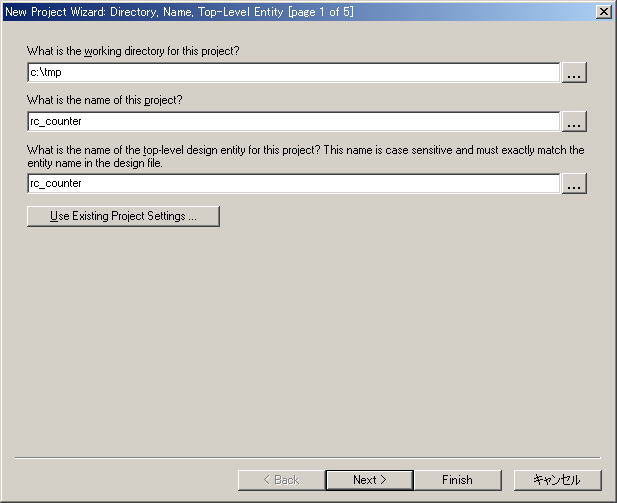

Quartus2を立ち上げ、ツールバーの「File -> New Project Wizard」でプロジェクトウィザードを起動します。

ディレクトリやプロジェクト名を指定します。

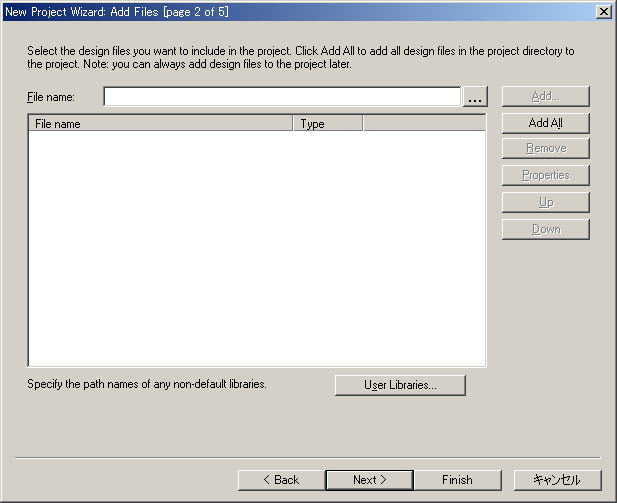

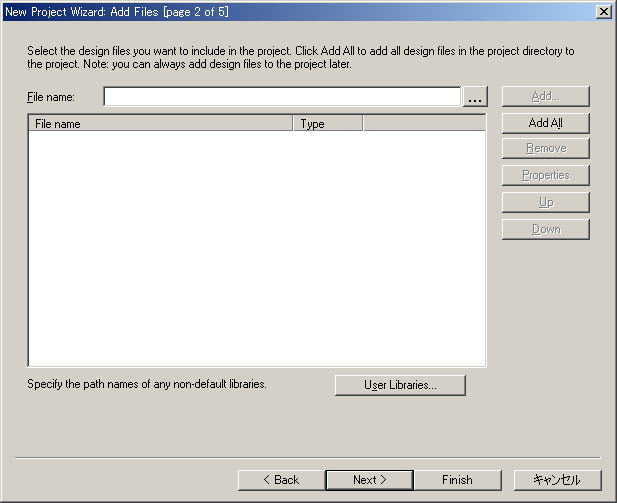

「Next」を押すと次の画面に進み、プロジェクトに追加するファイルを指定できますが、

とりあえずここは何もせず「Next」で次に進みます。

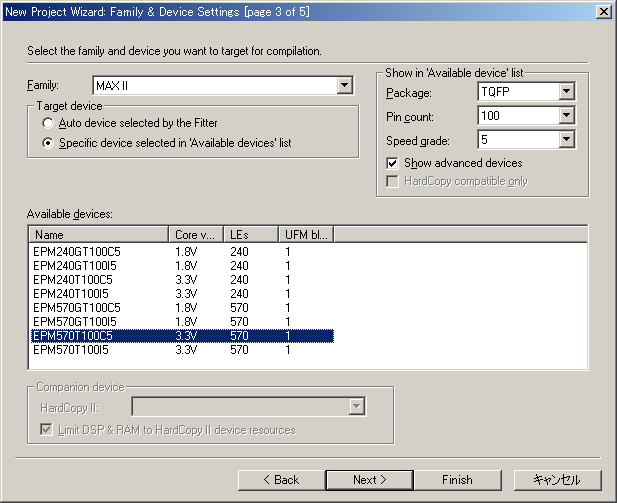

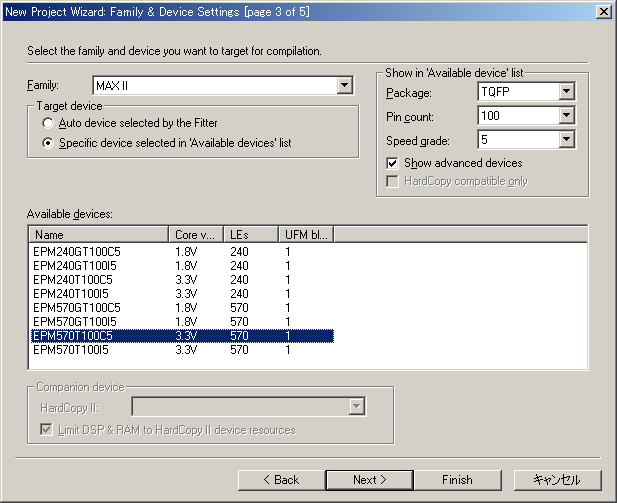

デバイスファミリーは「MAXII」を指定します。

Packageは「TQFP」、Pin countは「100」、Speed gradeは「5」をそれぞれ選択します。

「Next」で次の画面に進みます。

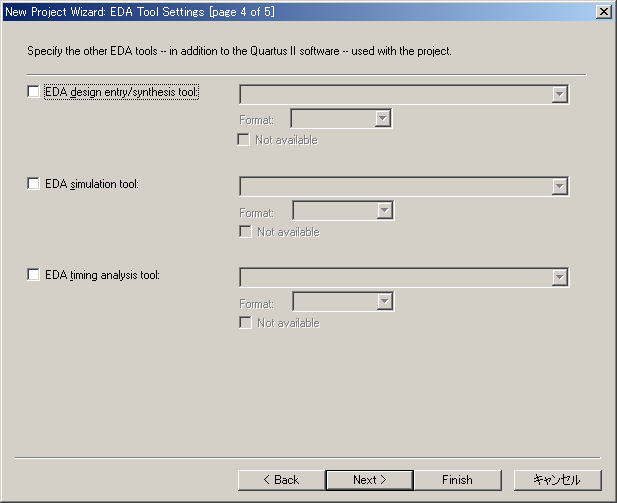

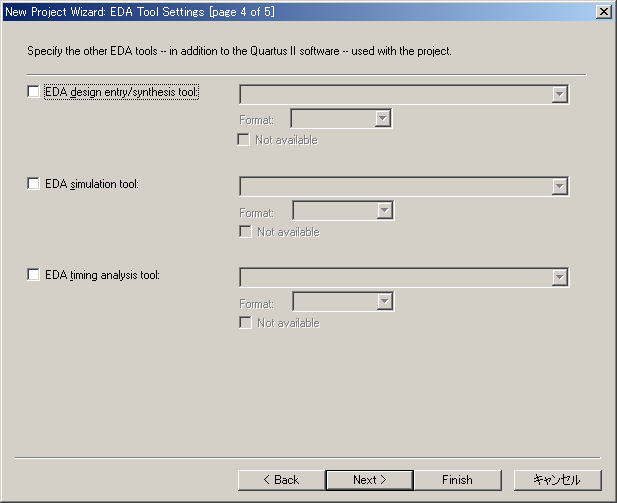

外部ツールの設定画面になりますが、Quartus2以外のツールは使用しませんので、

何も設定せずに「Next」で進みます。

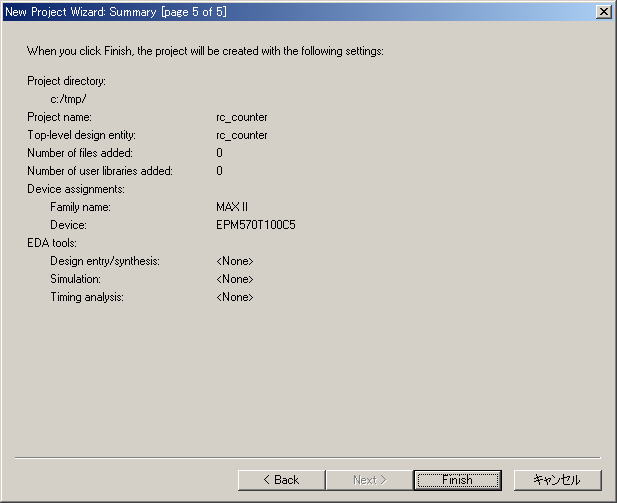

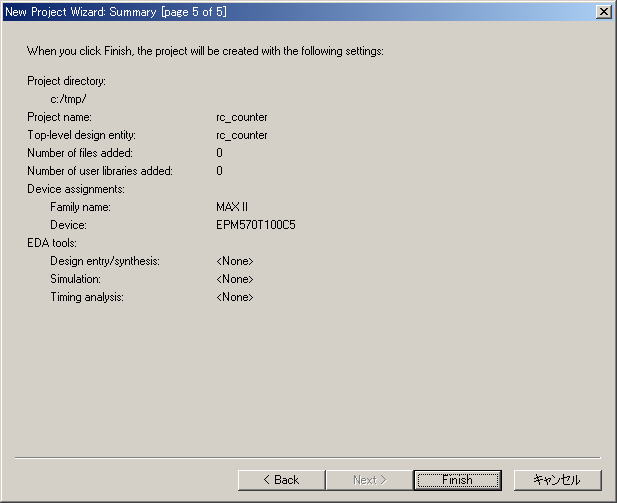

今まで設定したサマリーが表示されますので、問題なければ「Finish」で完了です。

<未使用ピンの設定>

新規プロジェクトを作成した際の未使用ピンのデフォルトの設定がGNDになっています。

このままでは、不注意で外部ロジックの出力ピンをGNDに落としてしまうトラブルが発生しかねません。

ですので、事前に未使用ピンが入力信号となるように設定しておきます。

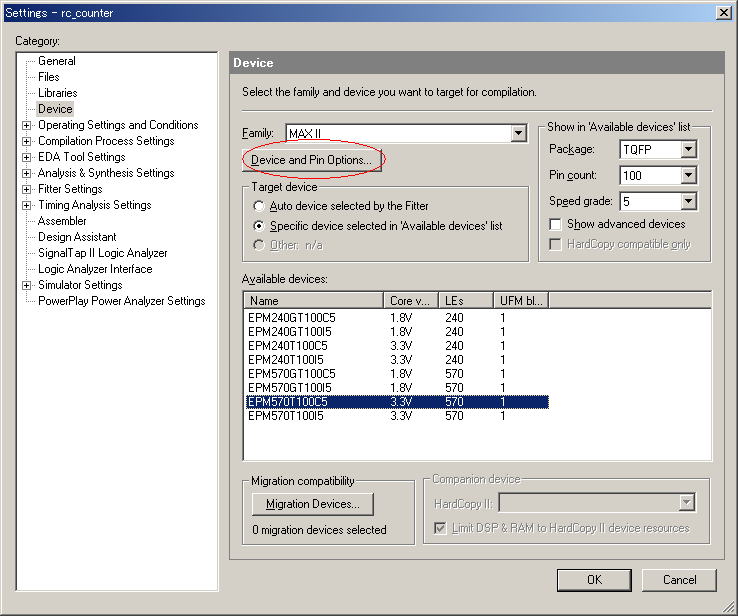

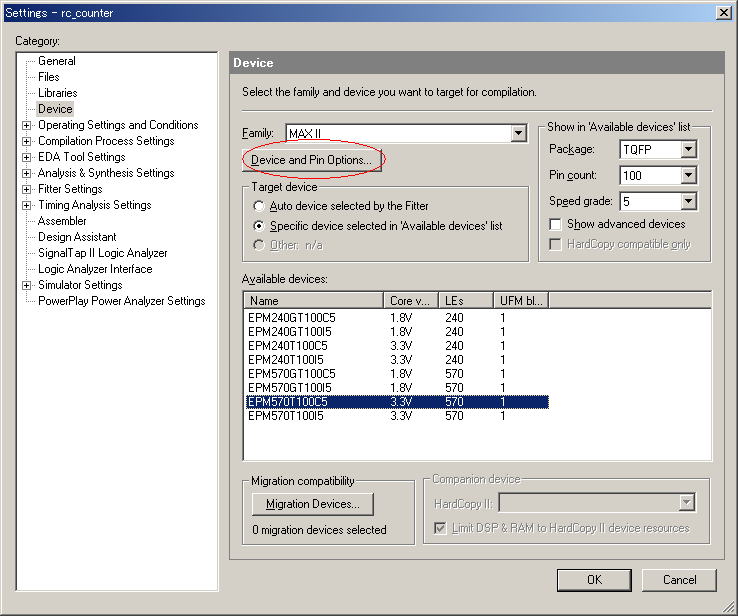

ツールバーの「Assignments -> Setting..」で設定画面を開きます。

Categoryは「Device」を選択して、「Device and Pin Options..」を押します。

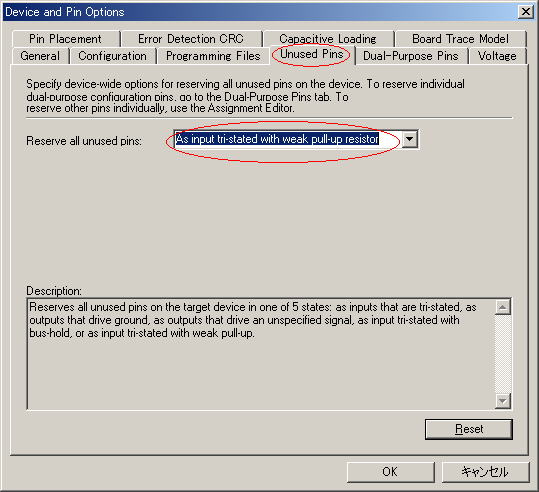

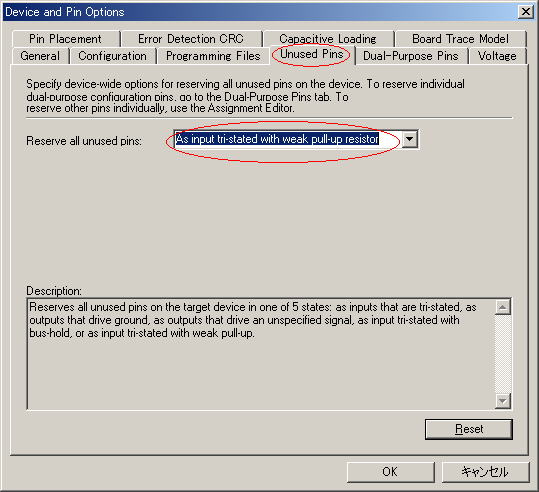

「Unused Pins」タブに切り替えて、「As input tri-stated with weak pull-up

registor」を選択します。

これで未使用ピンはプルアップ抵抗つきの入力ピンとして処理されます。

<Verilogソースの作成>

プロジェクトが作成されたので、プロジェクトを構成するソースファイルを作成します。

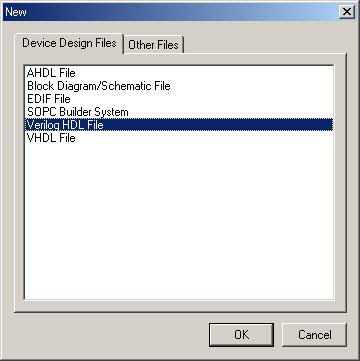

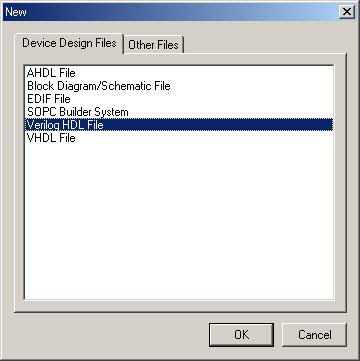

ツールバーの「File -> New」で下記の画面が開きます。

今回はVerilogを使用しますので、「Verilog HDL File」を選択して「OK」です。

このままの状態ではファイル名が”Verilog1”のようなQuartus2がつけたままの状態ですので、

ツールバーの「File -> Save As..」を開き、名前を”top”に変更します。

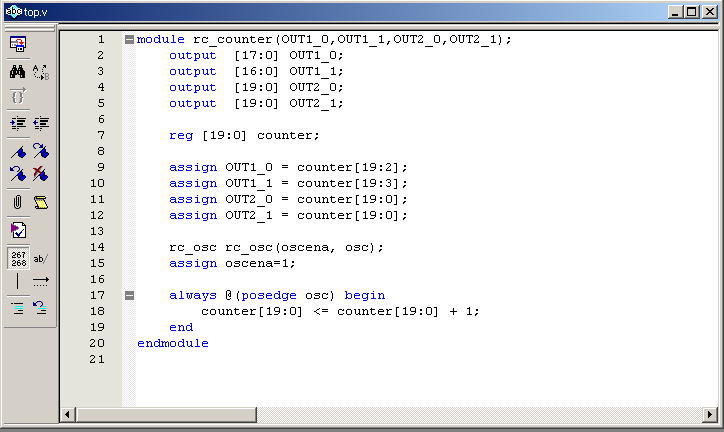

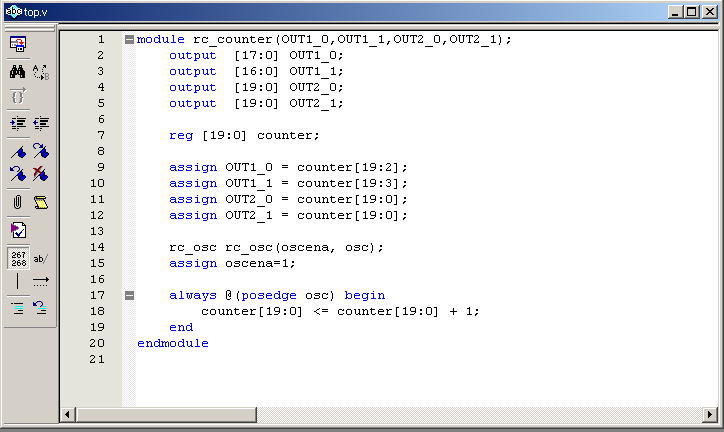

そして、下記のカウンターのVerilogソースを入力します。

20ビットカウンターを作り、バスOUT1_0,OUT1_1,OUT2_0,OUT2_1にカウンターの上位部分を出力するという単純な回路です。

クロックにRCオシレータのrc_osc()モジュールをインスタンス化して使用しています。

rc_osc()については次節で作成します。

<メガウィザード/メガファンクション>

RCオシレータやフラッシュメモリなどのFPGA/CPLD固有の機能や、乗算器、RAMなどの特定の機能を持つロジックはメガファンクションと呼ばれていて、メガウィザードを使用してVerilog/VHDLのソースとして作成します。

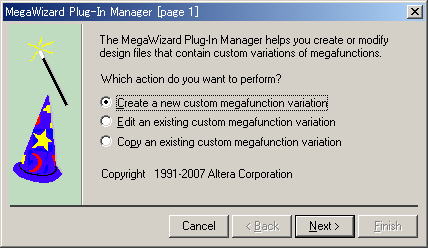

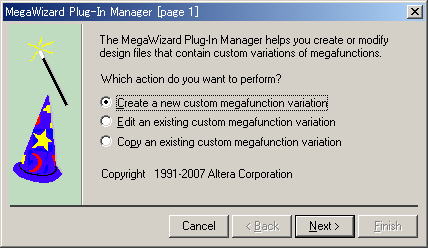

メガウィザードの起動はツールバーの「Tools -> MegaWizard Plug-In Manager..」を起動します。

「Create a new custom megafunction variation」を選択して「Next」。

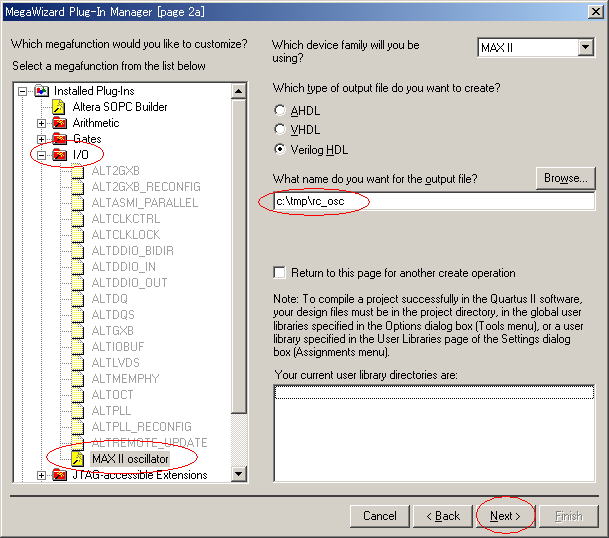

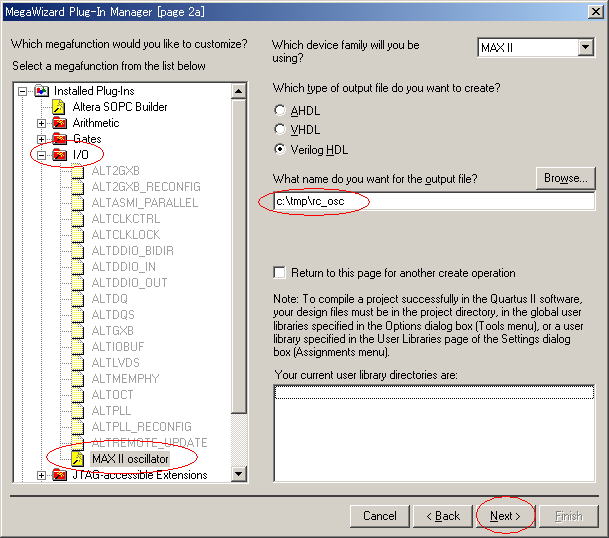

メガファンクションのカテゴリがツリー状に表示されますので「I/O」の中から「MAXII

oscillator」を選択します。

作成するソースは「Verilog HDL」で、ファイル名は「rc_osc」と入力します。そして「Next」。

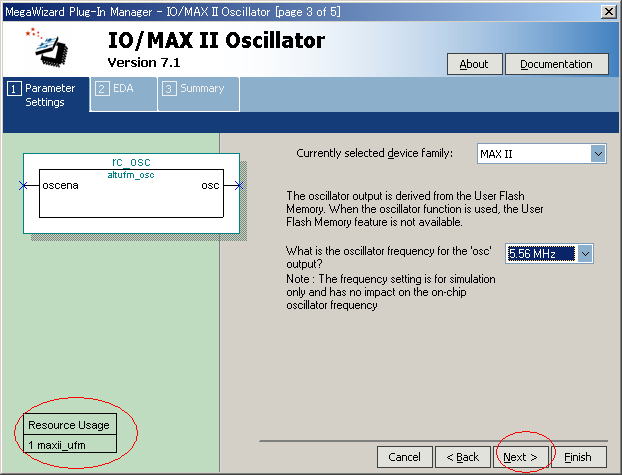

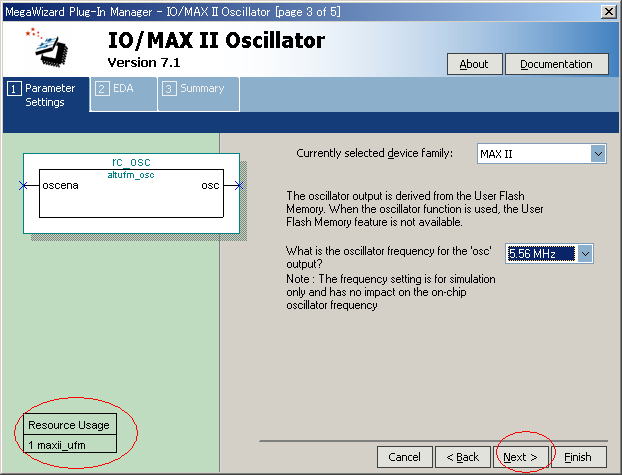

作成されたrc_oscのファンクション図が表示され、画面左下にこのファンクションを実現するのに必要なリソース(ロジックエレメントやufm)が表示されます。今回のRCオシレータではシュミレーション用の周波数のみを変更できますが、フラッシュメモリなどのファンクションの場合はビット幅などもこの画面で設定します。

rc_oscはoscenaを1にすると、oscからクロックが出力されるというものです。

今回はデフォルトのまま「Next」。

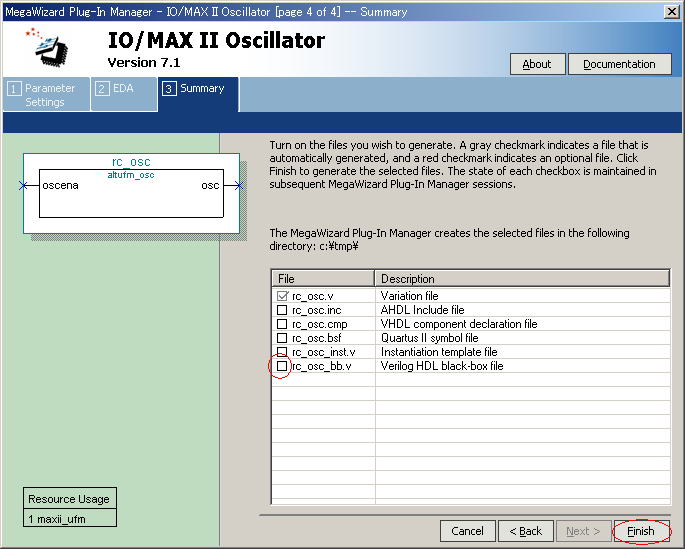

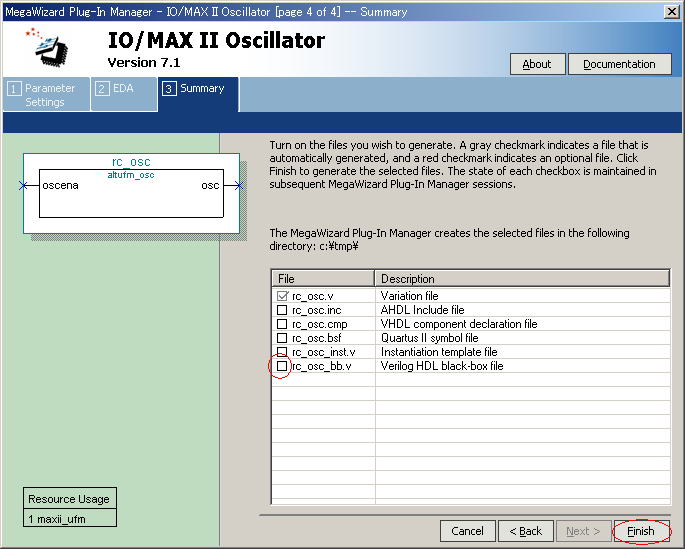

最後に作成されるファイルの確認画面が表示されます。

rc_osc.v は今回作成したRCオシレータの実態(Variation:変化物)ソースです。

このファイルをユーザが直接テキストエディタで修正することはしません。

デフォルトではrc_oscのインターフェイス部分だけ定義されたrc_osc_bb.vも作成するようになっていますが、

今回は必要ないのでチェックを外します。そして「Finish」で完了です。

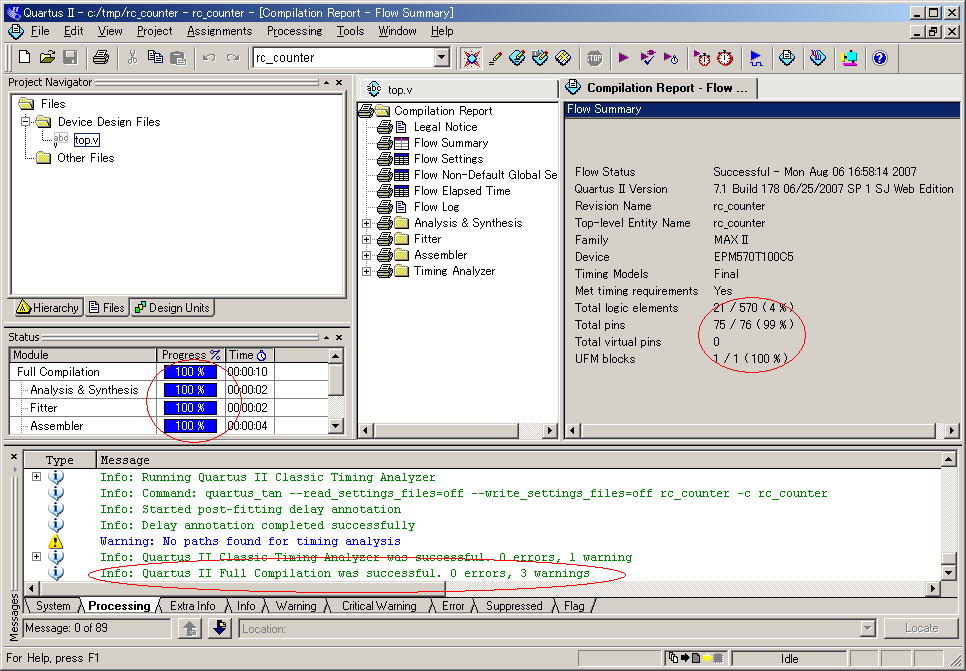

<コンパイル(論理合成)する>

これで今回のデザインに必要なソースが全て作成されましたので、Quartus2でコンパイルしてみます。

茶色の右向き再生矢印アイコンを押すか、ツールバーの「Processing -> Start

Compilation」で実行開始です。

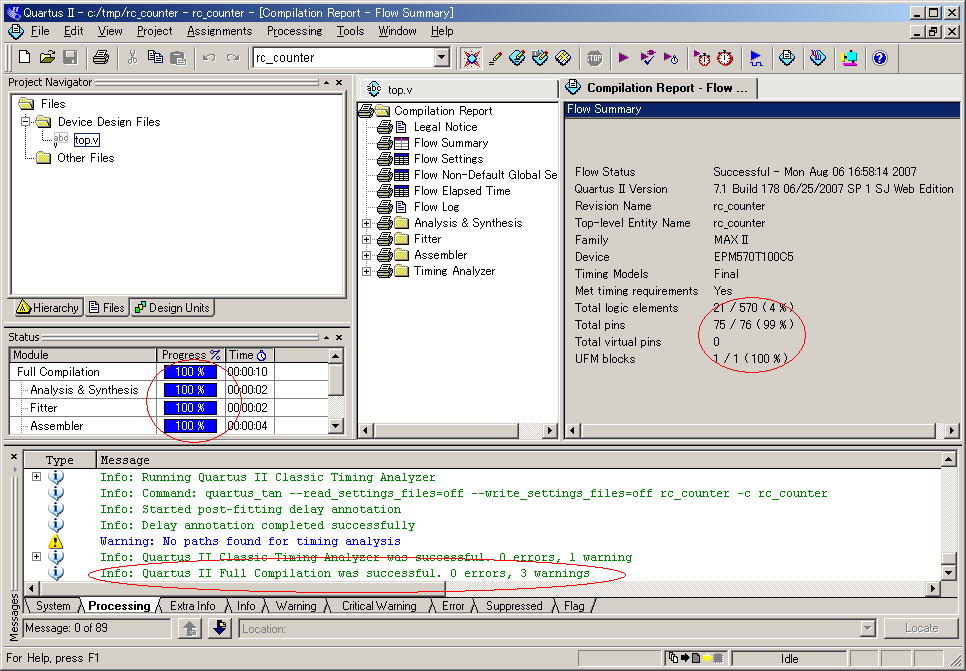

入力したソースコードにエラーがなければ、下記のような画面が表示され、コンパイルが完了します。

<ピン配置>

とりあえず論理合成が完了しているので、上記の結果をMAX2に書き込むことでカウンターは動作します。

ですがMAX2のピン配置はQuartus2が勝手に決めた状態になっています。

これでは困りますので、ピンの配置を指定することにします。

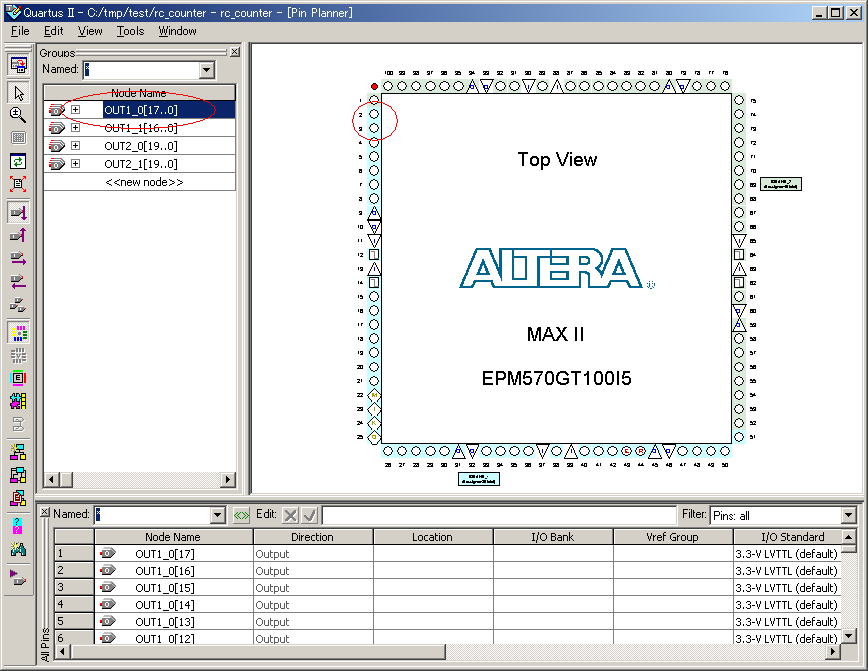

ピン配置を行う方法には、「Assignment Editor」か「Pin Planner」を使用します。

「Pin Planner」は実際にデバイスのピンを見ながらドラック・ドロップで配置することが出来るので、非常に便利です。

ここでは「Pin Planner」を使用することにします。ツールバーの「Assignments

-> Pins」で起動します。

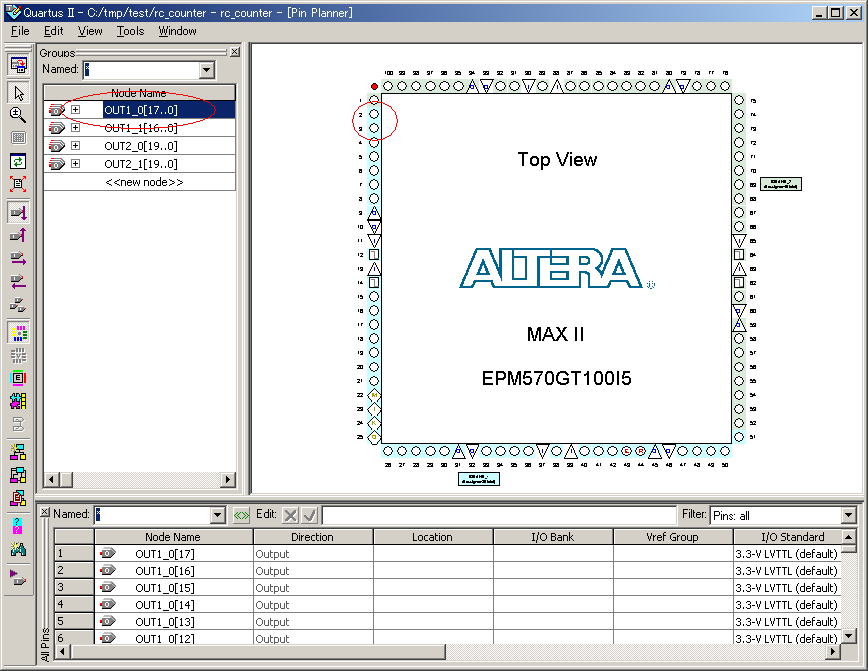

左側にデザインで使用している信号が表示され、右側にデバイスが表示されます。

基本動作は信号を選択状態(反転表示)にして、デバイスのピンにドラッグします。

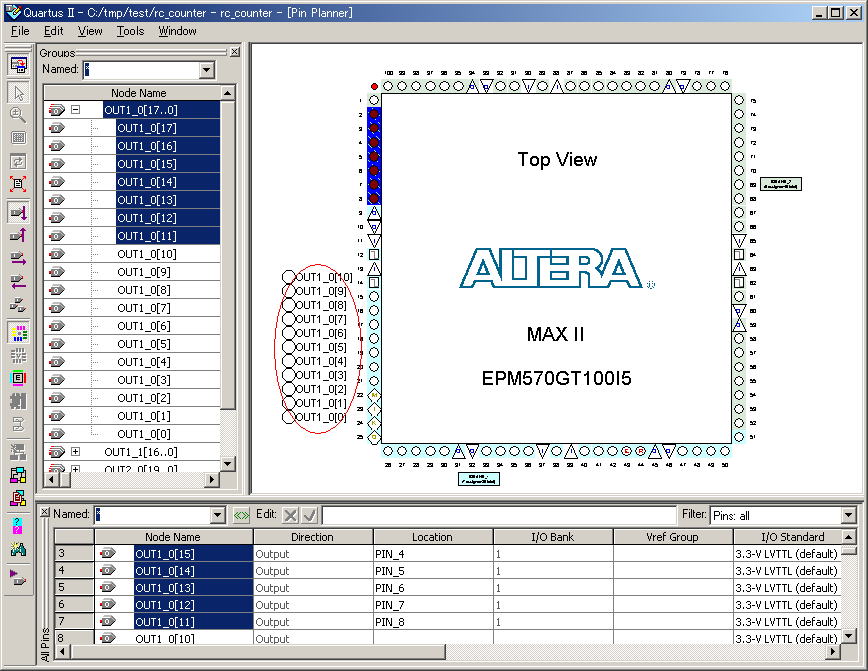

この際に、グループ信号(例えばOUT1_0[17..0])を選択して、まとめて配置することが出来るので便利です。

複数の信号をまとめて配置する場合には、どちらの方向(上・下・右・左)に向かって、配置するかを方向アイコンを選択しておくことで指定します。

OUT1_0[17..0]を選択して、デバイスのピン2にドラッグをします。このとき配置方向は下方向になりますので、下方向のアイコンをONにしておきます。

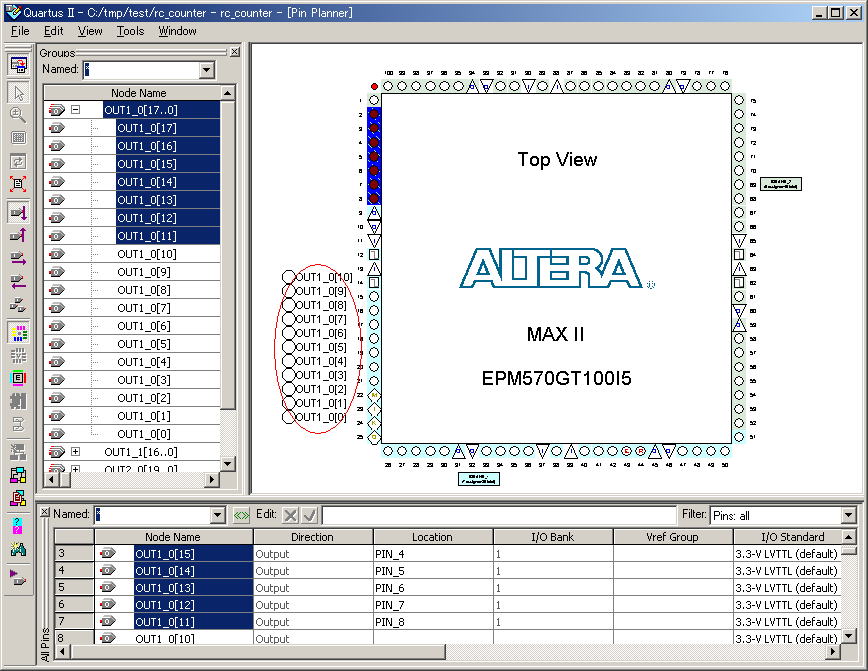

自動的にPIN2からPIN8までが配置されました。

PIN9はI/Oピンではないため、自動的配置されるのはPIN8までになり、一時停止状態になります。

この状態でPIN14をクリックすることで、残りの信号をPIN14から配置することになります。

このように信号を一本一本指定する必要がないため、効率よくピン配置が可能です。

上記の方法で全ての信号をI/Oピンに割り当てます。PIN_12は「MAX2 CPLDボード」の発振器の出力に接続されていますので、今回は割り当てをしないようにしています。(I/Oピンが1本あまります)

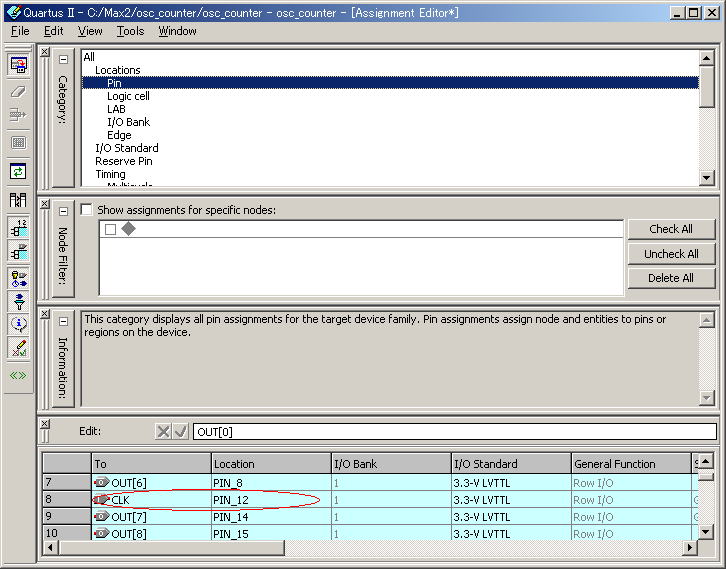

<グローバルクロックの設定>

今回のサンプルでは、クロックはMAX2内蔵のRCオシレータを使用するので関係ありませんが、FPGA/CPLDはクロック専用の入力ピン(グローバルクロックピン)が存在します。

「MAX2 CPLDボード」ではオシレータの出力が、グローバルクロックPIN12(GCLK)に接続されています。

グロバールクロックピンから入力されたクロック信号はFPGA/CPLDないの全てのロジックエレメントに効率よく伝達されるように設計されていますので、クロックを入力する場合にはグローバルクロックピンを使用するようにします。

グローバルクロックを使用するためには、単にグローバルクロック信号ピンにクロックを入れるだけではなく、Quartus2にもグローバルクロックが入力されていることを認識させる必要があります。

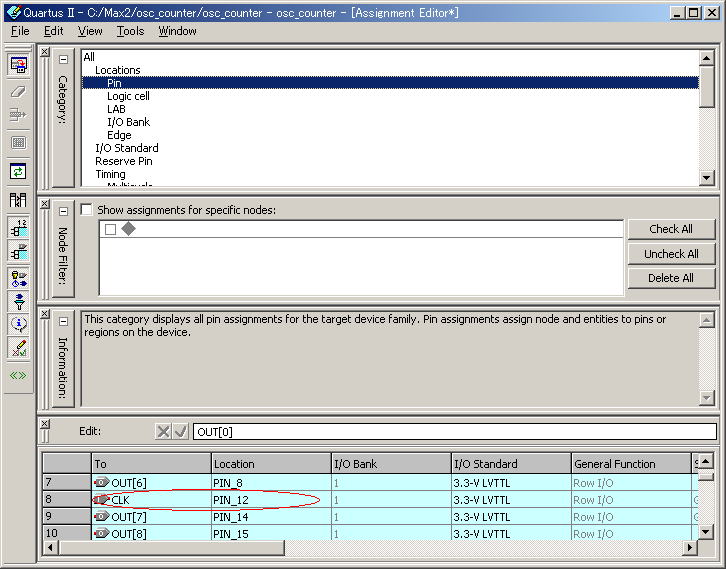

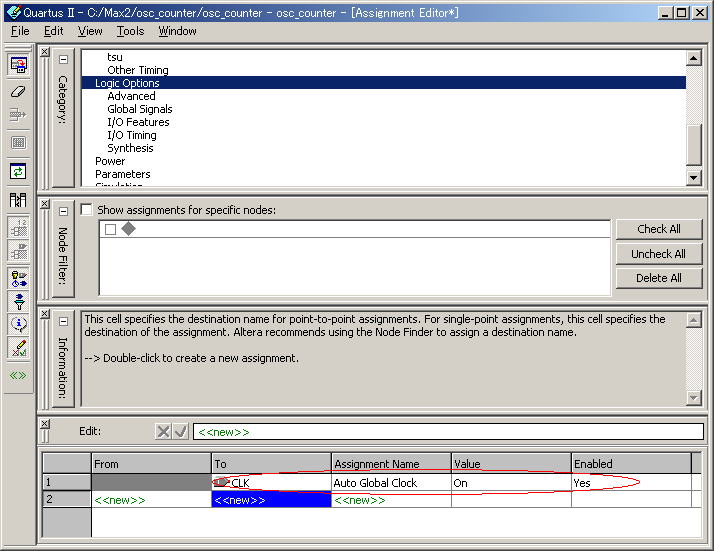

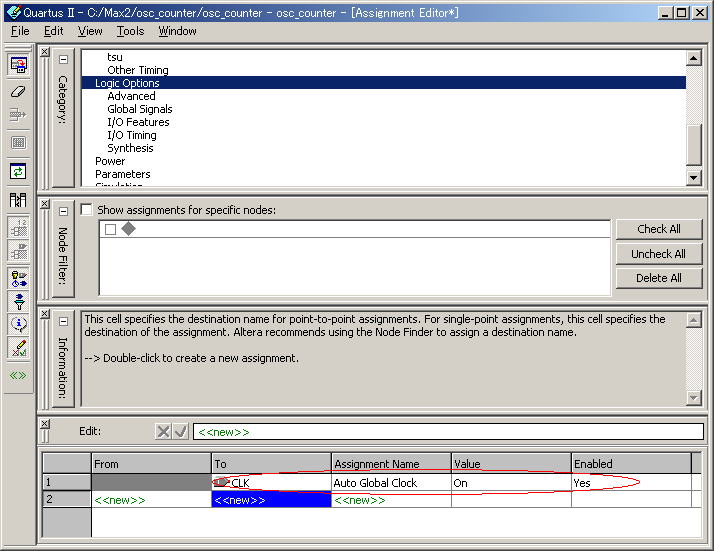

この手順を行うには、ツールバーの「Assignments -> Assignment Editor」を起動します。

CategoryをPinに設定して、ピン配置を確認します。

このデザインの場合はPIN_12に信号CLKが割り当てられています。

CategoryをLogic Optionsに変更して、

信号CLKに対して「Auto Global Clock」 「On」 「Yes」の設定を行います。

<デバイスの書き込み & 動作確認>

とりあえずここまでで、Verilogデザインの作成、ピン配置の指定、I/Oの設定まで出来ましたので、再度コンパイル(論理合成)を行います。

そして、「MAX2 CPLD」ボードに電源を入れて、JTAGライターとPCを接続してロジックを書き込みます。

(書き込み手順はこちらを参照 書き込みファイルを指定する手順(Change File)は不要です。)

書き込みが完了すると、MAX2の動作が開始されます。

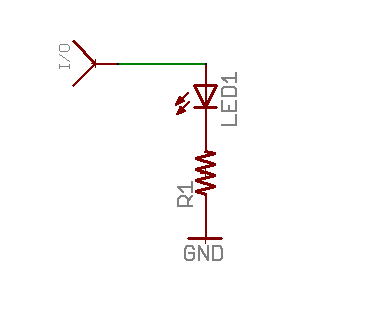

実際に動作を確認するには、次のいずれかの方法で行うことが出来ます。

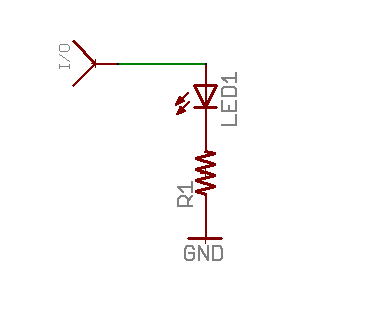

- オシロやロジアナを使ってI/Oピンの波形を見てみる

- 周波数が測定できるテスターなどで、GNDとI/Oピンの間の周波数を測定する(2MHz〜数十Hz)

- 抵抗(200-400Ω程度)と発光ダイオードをI/OピンとGNDの間に入れてみる

<JTAGを使って仮想スイッチやLEDを使う>

アルテラの提供するメガファンクションの中に、JTAGを使った「In-System Sources

and Probes」というものがあります。

これはJTAGを使ってユーザのデザインに対して、信号を入れる(Sources)、信号を見る(Probes)の機能を提供するものです。

市販のFPGA/CPLD評価基板にはよく、LEDやスイッチがついていて、ユーザのデザインの動作確認が簡単に出来るようになっています。

実はこの「In-System Sources and Probes」を使うことで、JTAGライター経由で同じようなことが簡単に出来ます。

PC上に仮想スイッチやLEDを作るのです。

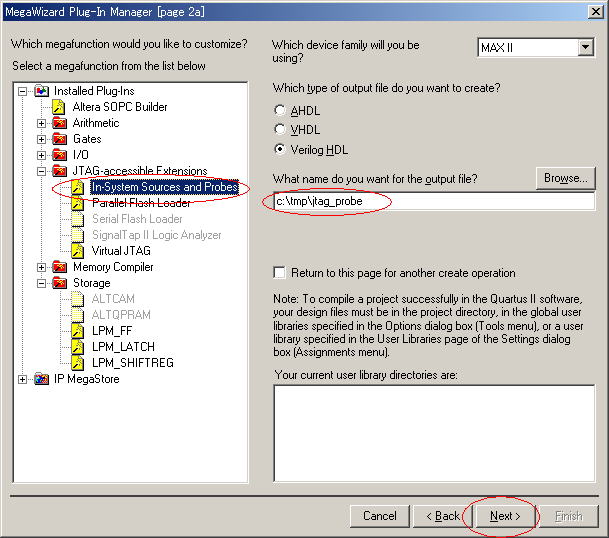

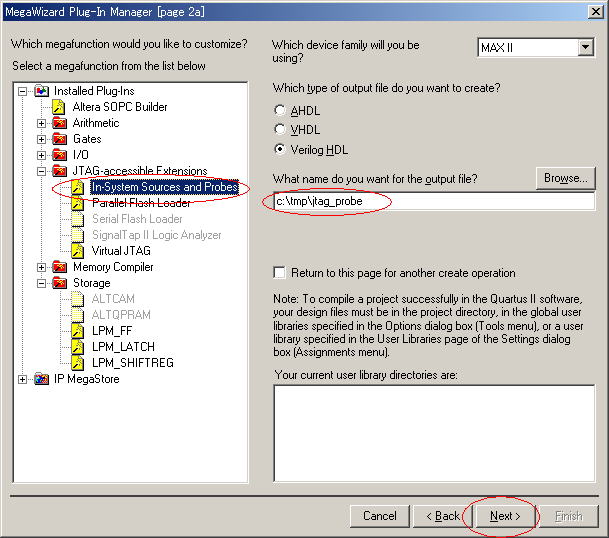

まずはツールバーから「Tools -> MegaWizard Plug-In Manager..」を起動します。

そして「JTAG-accessible Extensions」の中から「In-System Sources and Probes」を選択します。

output fileには「jtag_probe」と入力して「Next」です。

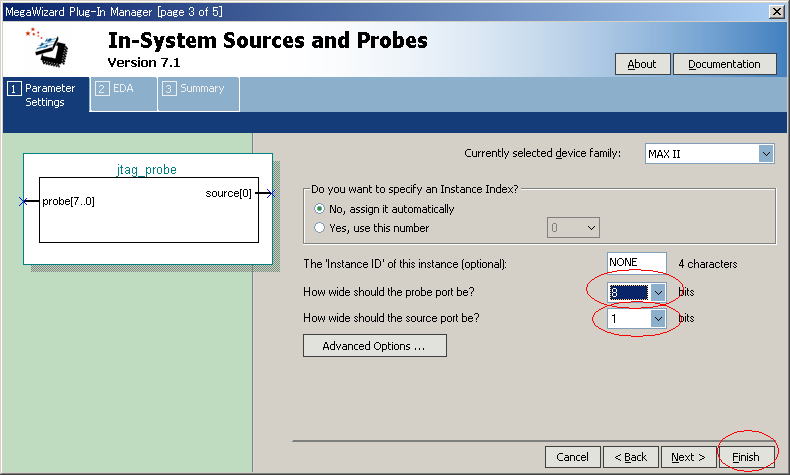

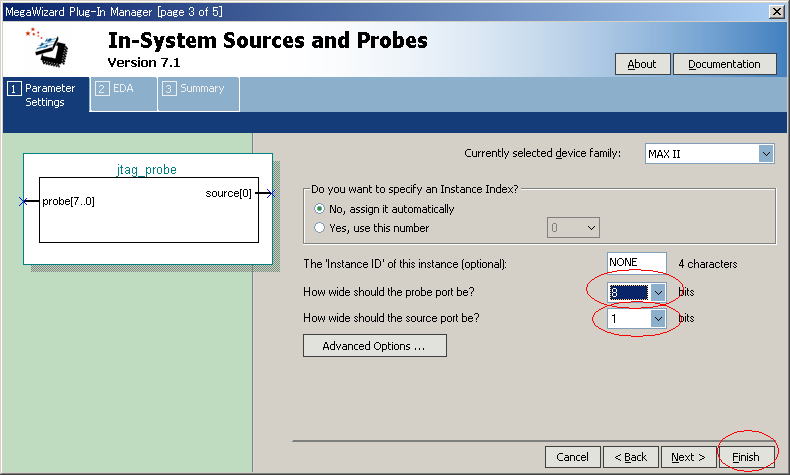

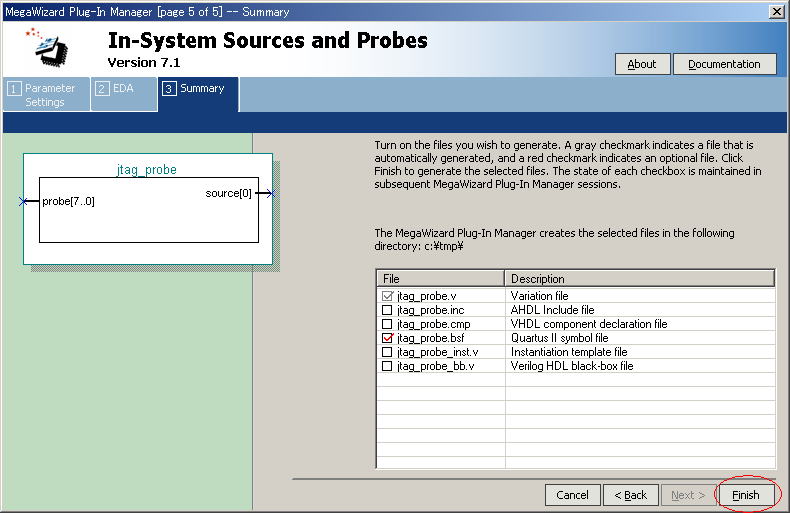

メガファンクション「In-System Sources and Probes」の構成を設定します。

今回はprobeを8bit、sourceを1bitに設定します。

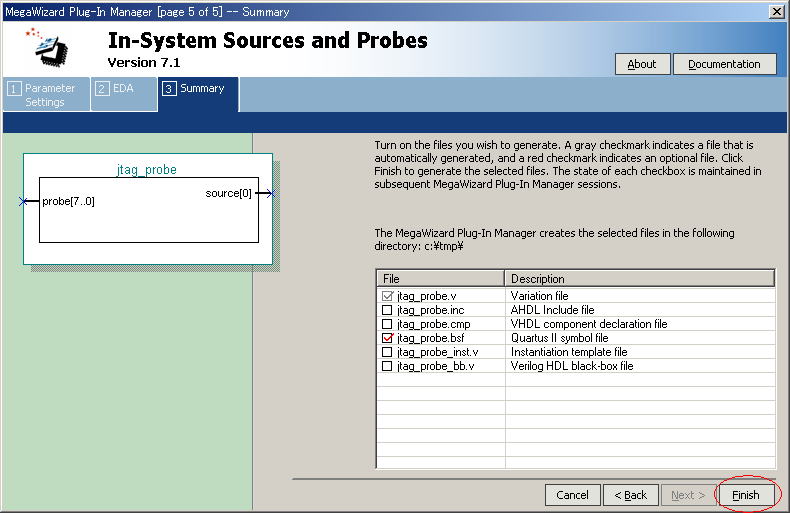

そして最後に[Finish」で終了です。

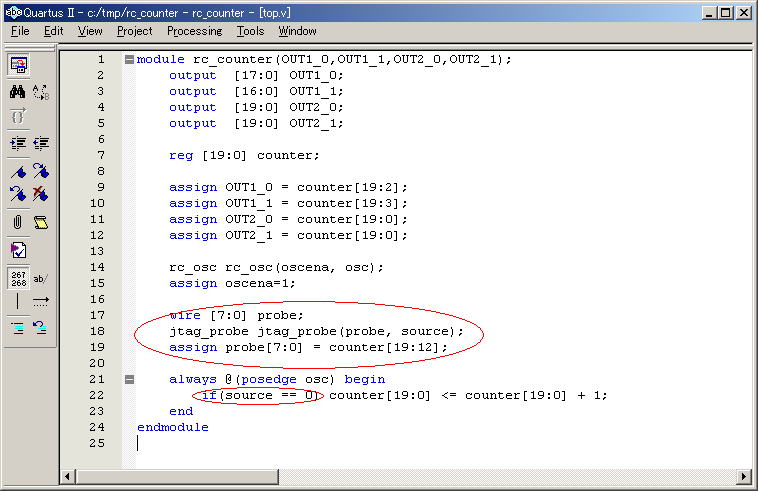

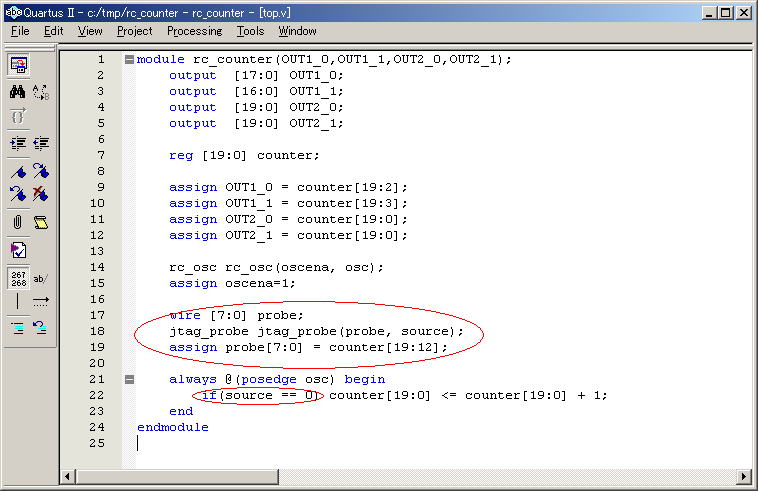

Verilogのソースファイルも「In-System Sources and Probes」に対応するように修正します。

これでデザイン関連の修正はOKですので。

コンパイル(論理合成)を行ってMAX2に「In-System Sources and Probes」を組み込んだデザインを書き込んでおきます。

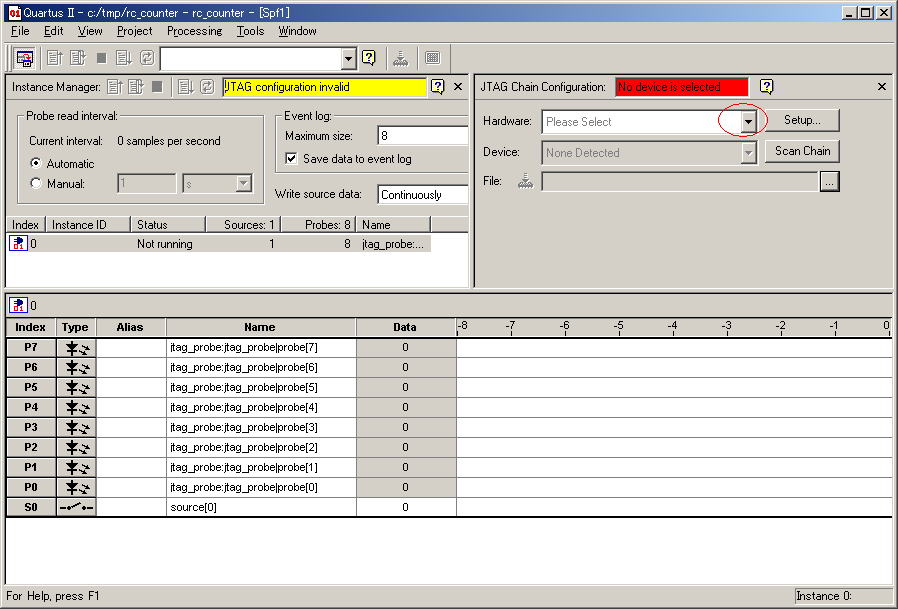

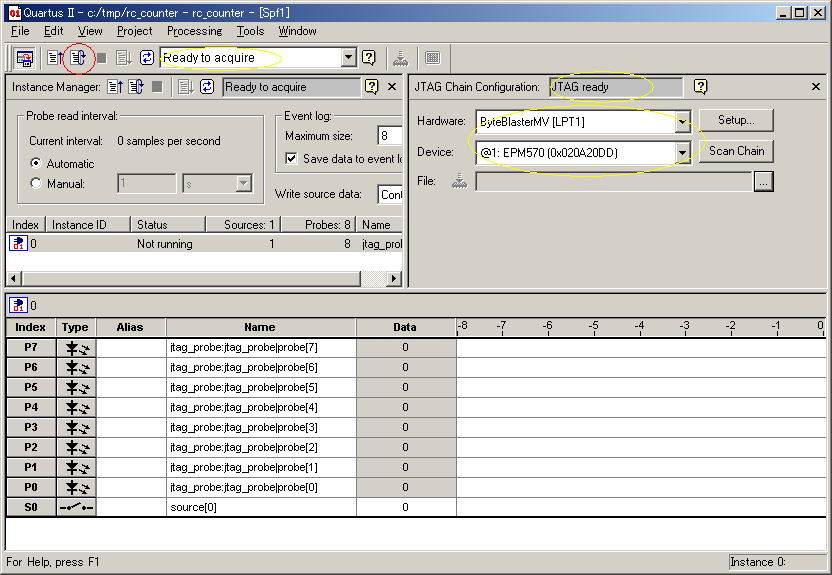

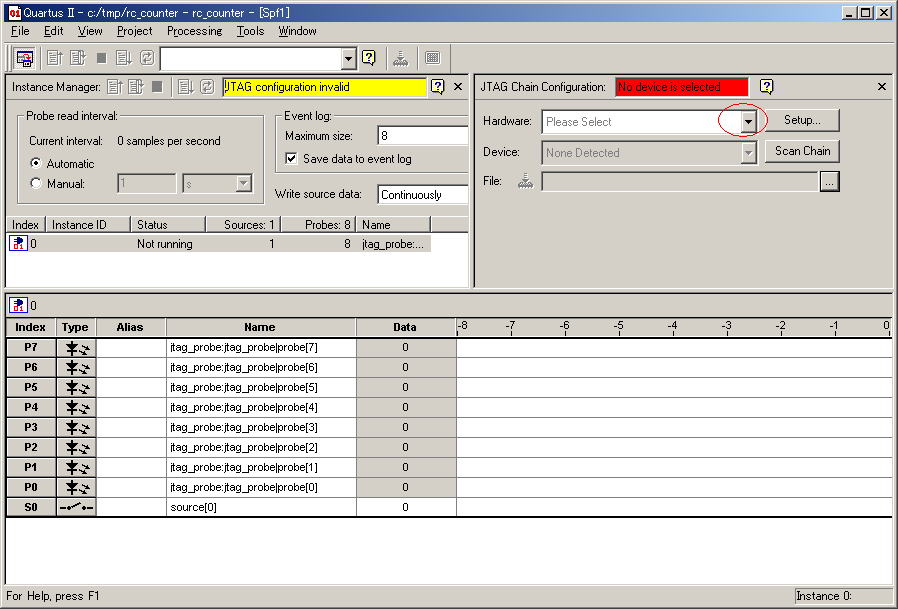

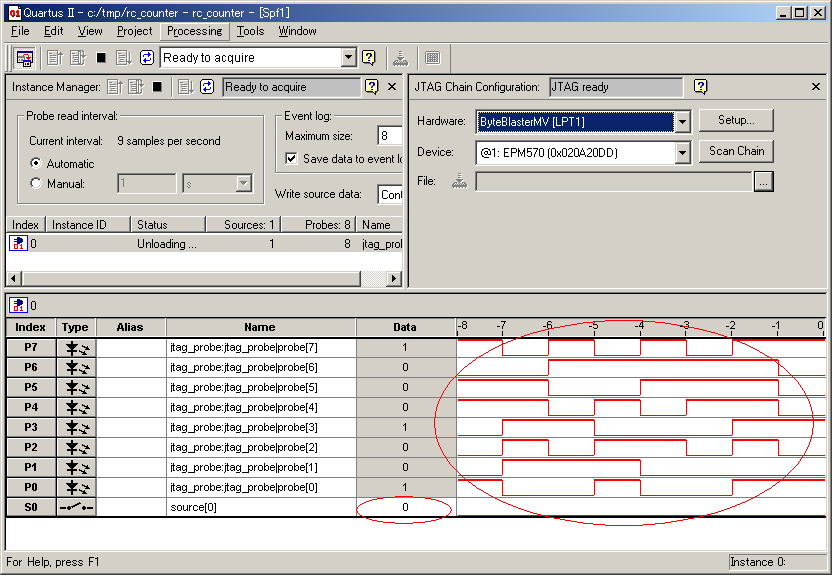

ツールバーの「Tools -> In-System Sources and Proes Editor」を起動します。

起動した状態ではJTAGライターが選択されていませんので、Hardwareのプルダウンメニューから「Byte

Blaster MV」を選択します。

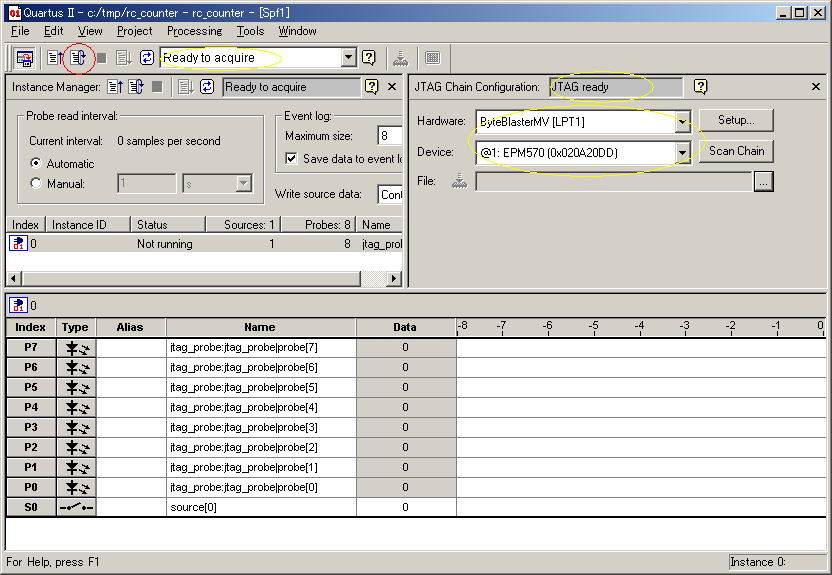

JTAGライターが選択されると、自動的にデバイスを認識します。ステータスも「Ready」になります。

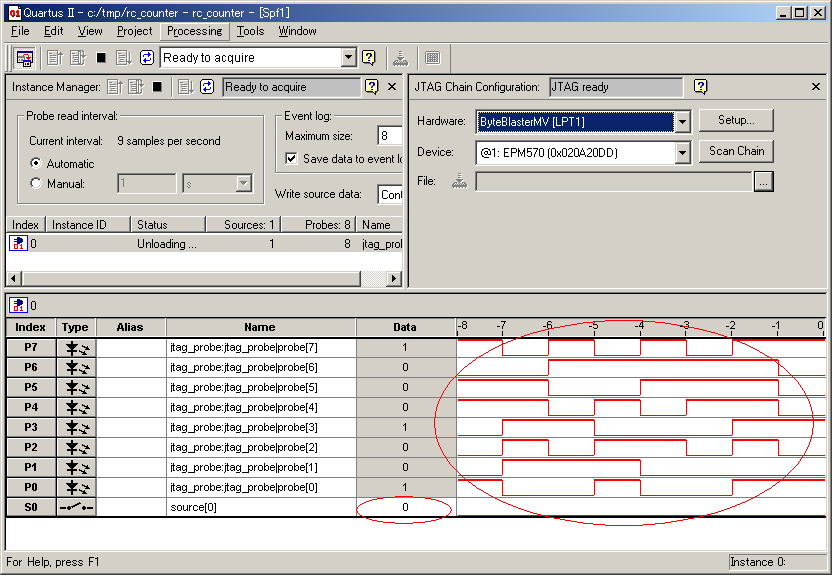

この状態で画面右上の「Continiously Read Probe Data」アイコンをクリックします。

画面右下にカウンターの値が順次表示されます。

キャプチャ速度がそれほど高速ではないため、カウントアップしている様子は確認できませんが、

カウンタが動作していることは確認できます。

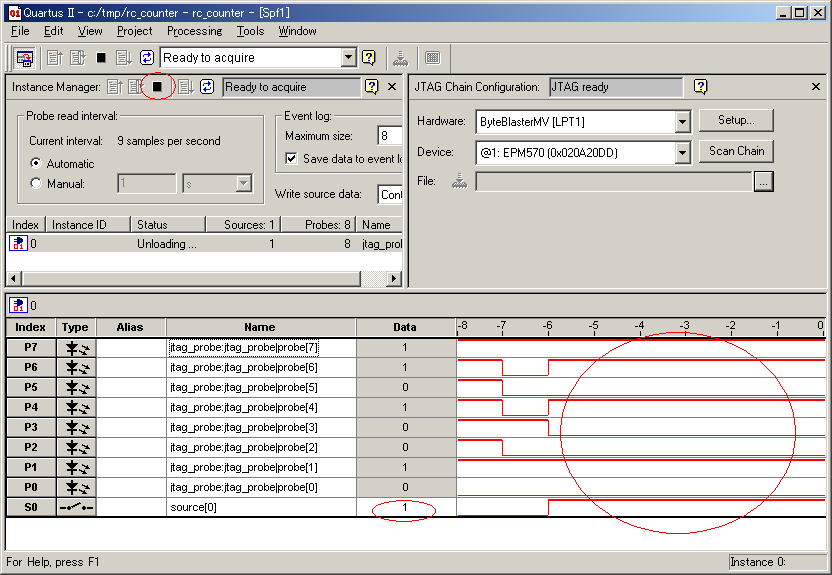

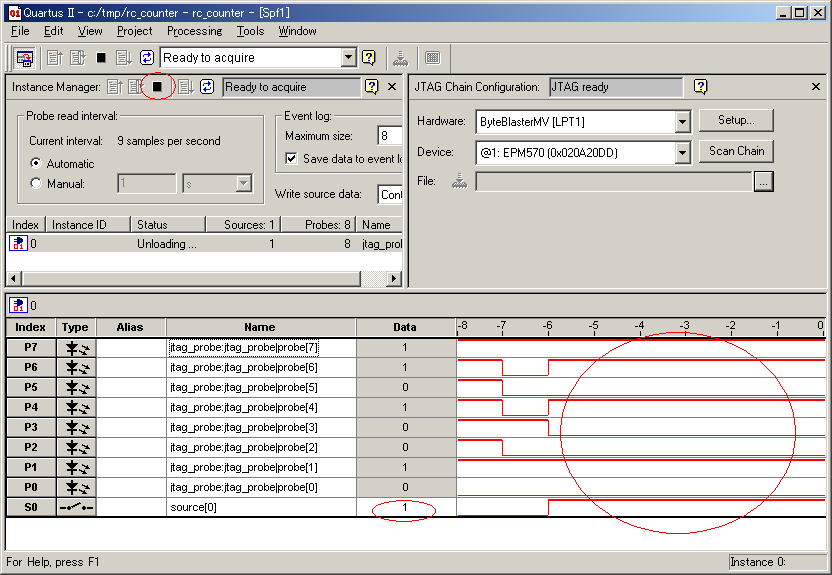

この状態で画面下中央の「S0」の「0」の値をクリックして、「1」に変化させます。

すると今まで変化していたカウンタが変化しなくなります。

これはVerilogソースの22行目でsourceが'0'の場合のみカウントアップするようにしているため、このようになります。

ちなみにこの「In-System Sources and Probes」を使うことで、MAX2の使用ロジックエレメント数は100以上増加します。

ロジックに空きがある場合には便利な機能だと思います。