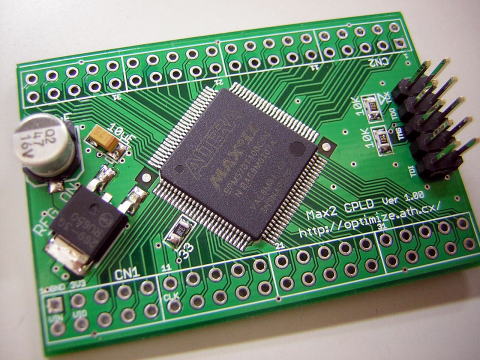

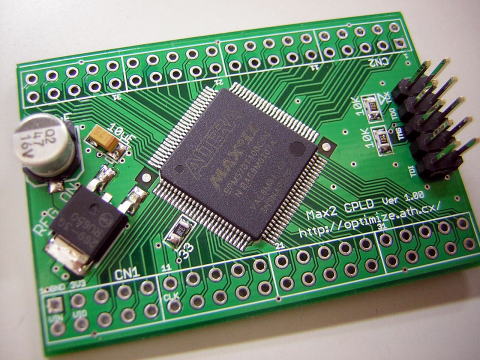

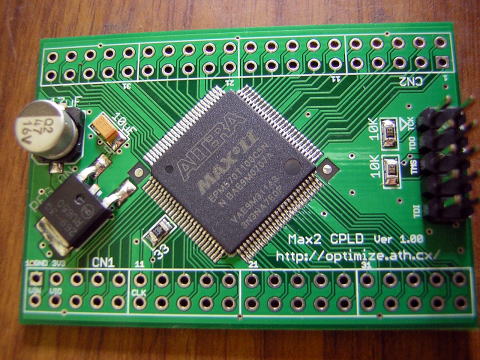

MAX2 CPLDボード

FPGA/CPLDはロジック回路をプログラムすることで非常に便利に使えるデバイスです。

今日のデジタル家電や携帯電話などの通信機器などに使用されていて、今後更に重要なデバイスとなることは間違いないでしょう。

ロジックを書き換えることで様々な用途に使用できるため、小ロット生産・アマチュアユース・教育用などに適しているのですが、評価ボードが割と高価なためなかなか手を出しにくいのが現状かと思います。

そこで、オプティマイズでは必要最小限の機能に限定し、価格を安くすることで、ピッチ変換基板を使うような手軽さで使用できるボードを開発しました。

MAX2はそれほど最近のデバイスではありませんが、8Kbitのフラッシュメモリ、内蔵RCオシレータ、3.3V/2.5V/1.8V/1.5Vのロジックレベルをサポート、低消費電力、ホットスワップ対応など多彩な機能を持ちます。

もちろんCPLDですので、外部にコンフィグ用のROMを用意する必要もなく、高いセキュリティーが期待できます。

<MAX2 CPLDボードの特徴>

<回路図>

回路図(PDF)

| CN2 | CN1 | |||||||

| PIN_1 | 40 | 39 | PIN_100 | GND | 1 | 2 | VIN | |

| PIN_99 | 38 | 37 | PIN_98 | +3V3 | 3 | 4 | EVCCIO | |

| PIN_97 | 36 | 35 | PIN_96 | PIN_2 | 5 | 6 | PIN_3 | |

| PIN_95 | 34 | 33 | PIN_92 | PIN_4 | 7 | 8 | PIN_5 | |

| PIN_91 | 32 | 31 | PIN_89 | PIN_6 | 9 | 10 | PIN_7 | |

| PIN_87 | 30 | 29 | PIN_86 | PIN_8 | 11 | 12 | GCLK0(PIN_12) | |

| PIN_85 | 28 | 27 | PIN_84 | PIN_14(GCLK1) | 13 | 14 | PIN_15 | |

| PIN_83 | 26 | 25 | PIN_82 | PIN_16 | 15 | 16 | PIN_17 | |

| PIN_81 | 24 | 23 | PIN_78 | PIN_18 | 17 | 18 | PIN_19 | |

| PIN_77 | 22 | 21 | PIN_76 | PIN_20 | 19 | 20 | PIN_21 | |

| PIN_75 | 20 | 19 | PIN_74 | PIN_26 | 21 | 22 | PIN_27 | |

| PIN_73 | 18 | 17 | PIN_72 | PIN_28 | 23 | 24 | PIN_29 | |

| PIN_71 | 16 | 15 | PIN_70 | PIN_30 | 25 | 26 | PIN_33 | |

| PIN_69 | 14 | 13 | PIN_68 | PIN_34 | 27 | 28 | PIN_35 | |

| PIN_67 | 12 | 11 | PIN_66 | PIN_36 | 29 | 30 | PIN_38 | |

| PIN_64(GCLK3) | 10 | 9 | PIN_62(GCLK2) | PIN_40 | 31 | 32 | PIN_41 | |

| PIN_61 | 8 | 7 | PIN_58 | PIN_42 | 33 | 34 | PIN_43 | |

| PIN_57 | 6 | 5 | PIN_56 | PIN_44 | 35 | 36 | PIN_47 | |

| PIN_55 | 4 | 3 | PIN_54 | PIN_48 | 37 | 38 | PIN_49 | |

| PIN_53 | 2 | 1 | PIN_52 | PIN_50 | 39 | 40 | PIN_51 | |

<スペック>

基板寸法: 約52.5mm x 36mm 高さ 約8mm(JTAGピンヘッダ未実装状態)

2.54mmピッチのユニバーサル基板に実装可能

外形・コネクタ位置ガバーデータ

電源電圧:レギュレータ使用時 5V-9V

消費電力:ロジック回路、動作周波数に依存

<電源ピン>

| CN1-1 | GND |

| CN1-2 | VIN 主電源(5V〜9V) |

| CN1-3 | 3.3V レギュレータ出力 (Max 700mA) |

| CN1-4 | EVCCIO 外部I/O電源 (1.5V 1.8V 2.5V) ソルダージャンパーにて対応 |

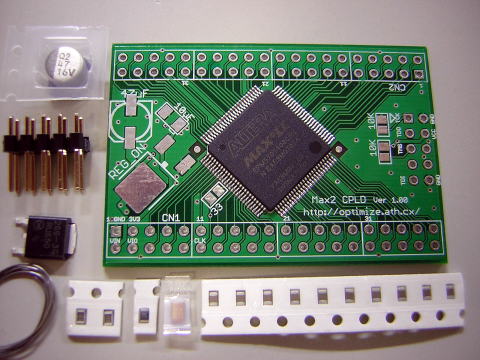

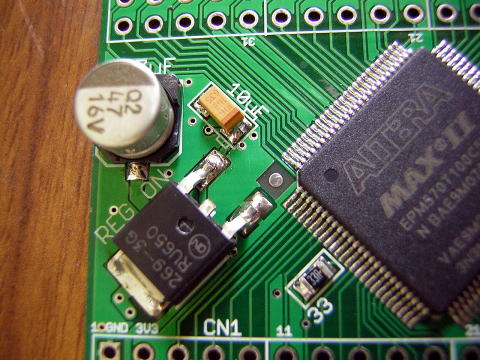

<製作>

キットが届きましたら部品を確認してください。

| 部品 | 数 | 備考 |

| 専用プリント基板 | 1 | EPM570T100C5 実装済み |

| 3.3V レギュレータ | 1 | MC33269-3.3 or LD1117-33 |

| チップコンデンサ 0.1uF | 10 | |

| 電解コンデンサ 100uF/16V | 1 | 極性あり |

| タンタルコンデンサ 10uF 16V | 1 | 極性あり |

| チップ抵抗 10KΩ | 2 | 103 |

| チップ抵抗 33Ω | 1 | 33R or 330 |

| JTAG用10ピンヘッダ | 1 | |

| 糸はんだ | 1 |

別途ピンヘッダやピンフレームをご用意ください。(40ピン2個 秋月電子にて購入可能)

20-30W程度の先端の細い半田ごて、ピンセット、ルーペ(虫眼鏡)、はんだを用意してください。

チップ部品のはんだ付けは、片側のランドにはんだを盛っておき、半田ごてではんだを溶かしながら、ピンセットでチップ部品を固定します。

ピンセットでチップ部品を飛ばしたりしないように注意してください。

半田付けのテクニックについてはこちらのページをご覧ください。

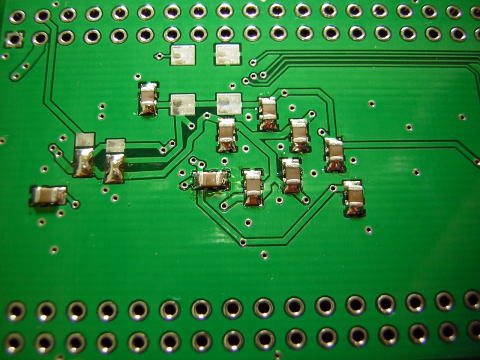

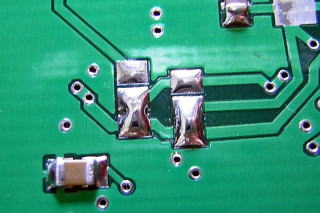

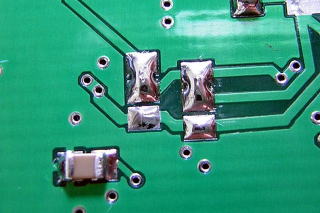

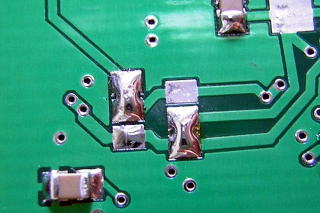

裏面のチップコンデンサ(全て0.1uF)から半田付けします。

<ソルダージャンパーの設定>

ソルダージャンパーは使用するI/O電源に合わせて設定します。

|

I/Oバンク1(CN1側)とI/Oバンク2(CN2側)のI/O電圧はレギュレータ出力の3.3Vを使用する。 (デフォルト設定:外部回路が3.3Vの場合) |

|

I/Oバンク1(CN1側)とI/Oバンク2(CN2側)のI/O電圧は外部I/O電源EVCCIO(CN1-4)を使用する。 (外部回路が全て1.8Vや2.5Vなどの場合) |

|

I/Oバンク1(CN1側)のI/O電圧はレギュレータ出力の3.3Vを使用し、I/Oバンク2(CN2側)は外部I/O電源EVCCIO(CN1-4)を使用する。 (CN2側に3.3V以外のデバイスを接続する場合) |

裏面の半田付けが終了したら、表面の半田付けをします。

背の低い部品から順次半田付けします。

(チップ抵抗・コンデンサ -> レギュレータ -> 電解コンデンサ -> JTAGコネクタ)

電解コンデンサ(47 or 100uF)、タンタルコンデンサ(10uF)は極性(向き)に注意。

レギュレータはタブ(耳:パッケージの上部)も含め、3ヶ所をしっかり半田付けする。

<動作確認>

これでキットの作成は完了ですが、実際に使用するためには「MAX2 CPLD」ボードに電源や外部部品を接続する必要があります。

動作確認ついては、実際にMAX2にロジックを書き込んで動作させてみるのが確実な方法です。

具体的な書き込み手順などは、JTAGライターのページで詳しく説明します。

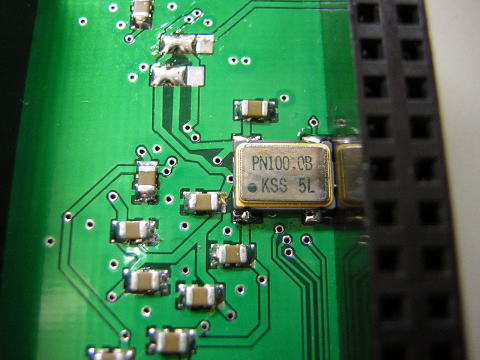

<オシレータ(オプション)>

オシレータはFXO-31FL(37FL)が使用できます。

フルタカパーツセンターのWEB通販で希望周波数のものを入手できます。

(注意:CN1とオシレータの位置が干渉しますので、コネクタを取り付けた後にオシレータを取り付けてください)