- `define DEBUG

- module spd_chk(FX2_SLOE, FX2_SLRD, FX2_SLWR, FX2_FD, FX2_FIFOADR, FX2_PKTEND,

- FX2_FLAGA, FX2_FLAGB, FX2_FLAGC, FX2_IFCLK,

- MODE, ADDR, RST, DIR,

- `ifdef DEBUG

- TP

- `endif

- );

|

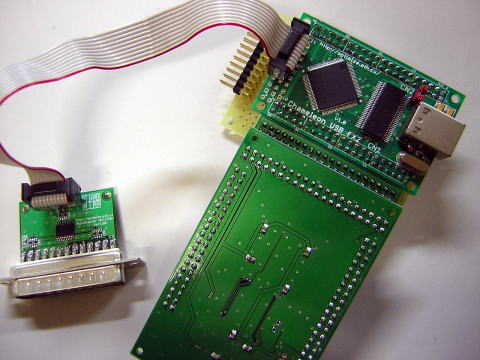

モジュール定義部分です。FX2_が先頭に付く信号は、「カメレオンUSB FX2」基板内部でFX2LPと接続されている信号ですので、全て記述しておきます。Qualtusツールの「Pin

Planner」ツールでMAX2のI/Oピンに割り当てます。

1行目のDEBUGがデファインされている場合は、TP(テストポート)信号が有効になります。私の場合はTPをロジアナに接続してデバッグを行っています。 |

- output FX2_SLOE;

- output FX2_SLRD;

- output FX2_SLWR;

- inout [7:0] FX2_FD;

- output [1:0] FX2_FIFOADR;

- output FX2_PKTEND;

- input FX2_FLAGA;

- input FX2_FLAGB;

- input FX2_FLAGC;

- input FX2_IFCLK;

|

| 4行目 のFIFO用データバスは8bitで使用します。MAX2のレジスタのリードライトにもこのバスを使用しています。 |

- `ifdef DEBUG

- output [11:0] TP;

- assign TP[0] = FX2_SLRD;

- assign TP[1] = FX2_SLWR;

- assign TP[2] = FX2_FLAGA;

- //assign TP[2] = cmp_err;

- assign TP[3] = FX2_FLAGB;

- assign TP[11:4] = FX2_FD;

- `endif

|

| デバッグ用の信号をTPに割り振っています。DEBUG時のみ有効になります。 |

- `define MODE_IDLE 0

- `define MODE_REGR 1

- `define MODE_REGW 2

- `define MODE_START 3

- input [1:0] MODE;

-

- input [1:0] ADDR;

- input RST;

-

- `define DIR_FX2PC 0

- `define DIR_PC2FX 1

- input DIR;

|

1−5行目は 動作モードをFX2LPからMAX2に伝えるための信号の定義です。(FX2LPのPD7、PD6と接続)

7行目はMAX2のレジスタを選択するためのアドレス線として使用します。(FX2LPのPD0、PD1と接続)

8行目はMAX2のリセット用信号として使用しています。(FX2LPのPD2と接続)

10-12行目はFIFOの転送方向をMAX2に伝えるために使用します。(FX2LPのPD3と接続) |

- reg [31:0] init_val;

-

- always @(posedge FX2_IFCLK)

- begin

- if(MODE == `MODE_REGW) begin

- if (ADDR == 0) init_val[7:0] <= FX2_FD;

- else if(ADDR == 1) init_val[15:8] <= FX2_FD;

- else if(ADDR == 2) init_val[23:16] <= FX2_FD;

- else if(ADDR == 3) init_val[31:24] <= FX2_FD;

- end

- end

|

| PCに送信するデータのシードを保持するレジスタinit_valの書き込み処理です。モードがMODE_REGWの時にFX2_FDバスからデータを取り込みます。FX2_FDバスは8bitですのでアドレス信号にて切り替えを行います。書き込みのタイミングにはIFCLKを使用しています。 |

- reg slwr,slrd;

- reg [31:0] cnt32;

- reg [30:0] wait_cnt31;

- reg [1:0] cnt2;

- reg [7:0] cnt32_8;

- reg cmp_err;

- reg first_skip; //first data is invalid

|

内部レジスタの定義です。

slwrはFIFO書き込み時に0になります。slrdはFIFO読み込み時に0になります。

cnt32は送信データ用の32bitカウンタです。

cnt2はcnt32を1byteずつ送信するためのカウンタです。

cnt32_8はcnt32をラッチする送信用の8bitバッファです。

cmp_errは受信データの正当性をチックし、正しくない場合に1になります。

first_skipは4同期転送時の受信タイミング調整用で、最初のクロックを無視するためのフラグです。 |

- always @(posedge FX2_IFCLK)

- begin

- if(RST) begin

- cnt32 <= init_val;

- wait_cnt31 <= 0;

- cnt2 <= 0;

- slwr <= 1;

- slrd <= 1;

- cmp_err <= 0;

- first_skip <= 1;

|

回路全体はIFCLKの立ち上がり信号による同期回路になります。

3−10行目でRST信号によるレジスタに初期値の設定を行います。

4行目はPCから書き込んだカウンタの種をカウンタにセットしています。 |

- end else if((((FX2_FLAGB == 1)&&(DIR == `DIR_FX2PC)) ||

- ((FX2_FLAGA == 1)&&(DIR == `DIR_PC2FX))) &&

- (MODE == `MODE_START)) begin

- if(DIR == `DIR_FX2PC) begin

- slwr <= 0;

- if (cnt2 == 0) cnt32_8 <= cnt32[7:0];

- else if(cnt2 == 1) cnt32_8 <= cnt32[15:8];

- else if(cnt2 == 2) cnt32_8 <= cnt32[23:16];

- else if(cnt2 == 3) cnt32_8 <= cnt32[31:24];

- if(cnt2 == 3) cnt32 <= cnt32 + 1;

- end

|

1−3行目 モードが転送モード(MODE_START)の場合に、FIFOの状況をFLAG信号でチェックして、FIFOに空き(あるいはデータが届いている)状態であれば、FIFOに書き込み(読み込み)を行います。

4−11行目 転送方向が(FX2 -> PC)の場合の処理。

slwrをアクティブにして、cnt2の値にしたがって、8bitレジスタcnt32_8にcnt32の内容をコピーします。4回コピーが終わったら、cnt32をインクリメント。 |

- if(DIR == `DIR_PC2FX) begin

- slrd <= 0;

- if((cnt2 == 1) && (FX2_FD != cnt32[ 7: 0])) cmp_err

<= 1;

- if((cnt2 == 2) && (FX2_FD != cnt32[15: 8])) cmp_err

<= 1;

- if((cnt2 == 3) && (FX2_FD != cnt32[23:16])) cmp_err

<= 1;

- if(first_skip == 0) begin

- if((cnt2 == 0) && (FX2_FD != cnt32[31:24])) cmp_err

<= 1;

- if(cnt2 == 0) cnt32 <= cnt32 + 1;

- end

- first_skip <= 0;

- end

|

転送方向が(PC -> FX2)の場合の処理。

slrdをアクティブにして、FIFOバスの内容に正しい値が入っているかチェックする。エラー時はcmp_errに1をセット。

slrdをアクティブにした最初のデータは無効なので、これをネグルためにfirst_skipを使用。 |

- cnt2 <= cnt2 + 1;

- end else begin

- if(MODE == `MODE_START) wait_cnt31 <= wait_cnt31 + 1;

- slwr <= 1;

- slrd <= 1;

- cnt2 <= 0;

- first_skip <= 1;

- end

- end

|

1行目 はcnt2レジスタのインクリメント。

3行目 転送開始状態なのに、FIFOが一杯(空)のため待ちの場合は、wait_cnt31をインクリメント。

4−7行目 転送が行われないときの状態をセット。 |

- wire [7:0] reg_data;

- assign reg_data = (ADDR == 0) ? wait_cnt31[7:0] :

- (ADDR == 1) ? wait_cnt31[15:8] :

- (ADDR == 2) ? wait_cnt31[23:16] : { cmp_err, wait_cnt31[30:24]

};

-

- wire [7:0] fifo_data;

- assign fifo_data = cnt32_8;

-

- assign FX2_SLOE = ((MODE == `MODE_START)&&(DIR == `DIR_PC2FX)) ? 0 : 1;

- assign FX2_FIFOADR = (DIR == `DIR_FX2PC) ? 2 : 0;

- assign FX2_PKTEND = 1;

- assign FX2_SLRD = slrd;

- assign FX2_SLWR = slwr;

- assign FX2_FD =

- ((MODE == `MODE_REGW) || ((MODE == `MODE_START) && (DIR ==

`DIR_PC2FX))) 8'bzzzzzzzz :

- (MODE == `MODE_REGR) ? reg_data : fifo_data;

-

- endmodule

|

1−4行目 MAX2レジスタ読出しのための定義、32bit目には検証結果cmp_errのフラグをセット。

9−16行目 モード状態、転送方向(DIR)の状態に応じて、FX2の制御信号をコントロールする。 |