SVFファイルの作成はQualtusIIのメニューから「Tools -> Programmer」(あるいはプログラマーアイコンをクリック)でQualtusII標準のプログラマーを起動します。

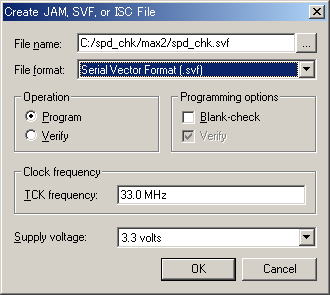

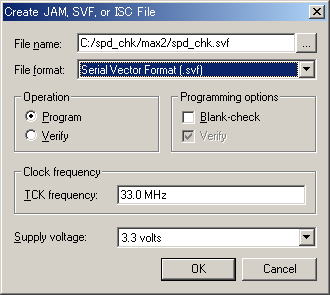

その状態でメニューから「File -> Create/Update -> Create JAM,SVF...」を起動すると下記の画面が表示されます。

この画面で「Serial Vector Format[.svf]」を選択して「OK」をクリックすればSVFファイルが作成されます。

<MAX2デザインツールQualtusII>

MAX2のロジック(デザイン)を開発するためにはアルテラ社が提供する無償で利用できるQualtusIIを使用します。

オプティマイズではMAX2単体の基板も開発しています。

QualtusIIのインストール手順については、Max2 CPLDボードのページをご参照ください。

<サンプルデザインの開発>

Max2 CPLDボードのページにサンプルデザインの開発例がありますので、そちらを参照してください。

(リンク先のサンプルはMax2 CPLDボード用のサンプルですので、実際に「カメレオンUSB FX2」には書き込まないでください。)

(「カメレオンUSB FX2」用のデザイン例はサンプルアプリケーションのページにあります。)

「カメレオンUSB FX2」では基板内でMAX2のIOとFX2LPのFIFO関連信号が接続されています。

このため、FX2LPで出力に設定した信号を、MAX2側でも出力に設定すると最悪ICが壊れます。

このことを防ぐために、必ずMAX2の未使用I/Oは「As input tri-stated with weak pull-up registor」に設定してください。

| MAX2 IO | FX2LP 信号 | MAX2 IO | FX2LP 信号 | |

| IO2 | PD5_FD13 | IO20 | PA4_FIFOADR0 | |

| IO3 | PD6_FD14 | IO21 | PA2_SLOE | |

| IO4 | PD7_FD15 | IO26 | CTL2_FLAGC | |

| IO5 | RDY0_SLRD | IO27 | CTL1_FLAGB | |

| IO6 | RDY1_SLWR | IO28 | CTL0_FLAGA | |

| IO7 | PD4_FD12 | IO29 | PB7_FD7 | |

| IO8 | PD3_FD11 | IO30 | PB6_FD6 | |

| CLK12_IO12 | CLKOUT | IO33 | PB5_FD5 | |

| CLK14_IO14 | IFCLK | IO34 | PB4_FD4 | |

| IO15 | PD2_FD10 | IO35 | PB0_FD0 | |

| IO16 | PD1_FD9 | IO36 | PB1_FD1 | |

| IO17 | PD0_FD8 | IO38 | PB2_FD2 | |

| IO18 | PA6_PKTEND | IO40 | PB3_FD3 | |

| IO19 | PA5_FIFOADR1 |

<MAX2デザインの書き込み>

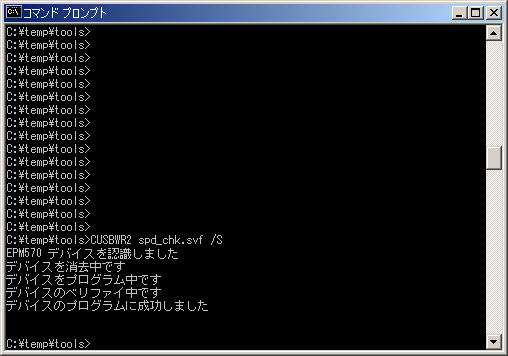

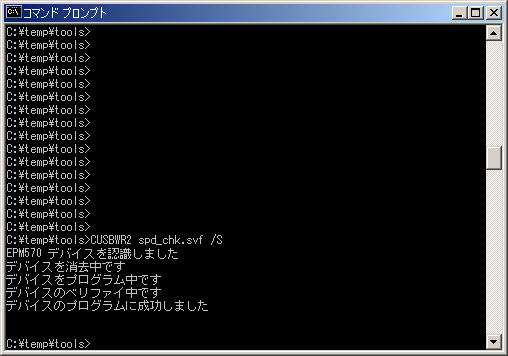

QualtusIIで開発したデザインはCUSBWR2ツールを使用してMAX2に書き込むことが出来ます。

CUBWR2はコンソールアプリケーションですので、Windowsのコンソール画面を開いて起動します。

使い方は「CUSBWR2 [SVFファイル] [/n] [/S] [/E]」となります。

| /n | n(数字)はカメレオンUSB FX2のID番号になります。 複数のカメレオンUSB FX2が接続されている場合、対象を選択するために使用します。 |

| /S | MAX2のデザインを読出し禁止に設定します。 他人にデザインをコピーさせないために使用します。 |

| /E | MAX2の消去のみを行います。SVFファイルの指定は不要(無効)です。 |

SVFファイルの作成はQualtusIIのメニューから「Tools -> Programmer」(あるいはプログラマーアイコンをクリック)でQualtusII標準のプログラマーを起動します。

その状態でメニューから「File -> Create/Update -> Create JAM,SVF...」を起動すると下記の画面が表示されます。

この画面で「Serial Vector Format[.svf]」を選択して「OK」をクリックすればSVFファイルが作成されます。